# COMMUNICATIONS IC Handbook

# Foreword

GEC Plessey Semiconductors (GPS) has a world-class reputation for ICs for radio frequency applications. GPS offer state-of-the-art ICs for cellular and cordless phones, cellular and cordless infrastucture, and pagers.

Originally supplying a range of radio parts such as amplifiers, synthesisers and prescalers, GPS has developed and enhanced its technologies to suit much higher system integration, and now offers some of the most advanced integrated circuits available. Today, GPS provides cost effective, high performance solutions for tomorrow's handheld radios, and even credit card sized pagers, with their emphasis on reduced size and minimum power consumption (to increase battery life).

GPS is one of very few companies with the complete range of semiconductor technology for the integration of a radio system:

- leading edge RF bipolar technologies with on-chip capacitors and inductors

- mixed signal CMOS for RF/IF (intermediate frequency) and voice processing and coding

- digital CMOS with a library of advanced functions such as the Pine and Oak DSPs and the ARM 32bit RISC microprocessor

- SAW Filter technology

- advanced packaging techniques.

With these, and with many years experience of implementing systems on silicon, GPS is ideally placed to support your IC requirements in the radio frequency arena.

This latest Communications Handbook details some of the latest developments in chipsets for analog cellular systems and for advanced pagers. It also introduces a wide range of Surface Acoustic Wave - SAW - Filters for digital cellular (such as GSM and PCS) and digital cordless (such as DECT) applications. Take a look at what's in there and give us a call!

# **Contents**

|              |                                                   | PAGE |

|--------------|---------------------------------------------------|------|

| Product List | - By Circuit Type                                 | 4    |

| Product List | - Alpha numeric                                   | 7    |

| Section 1:   | PLLs (Phased Lock Loop)                           | 9    |

| Section 2:   | Prescalers                                        | 35   |

| Section 3:   | Paging Receivers & Decoders                       | 59   |

| Section 4:   | Analog Cellular Components                        | 107  |

| Section 5:   | PCM Circuits                                      | 187  |

| Section 6:   | IF SAWs for GSM Digital Cellular Communications   | 213  |

| Section 7:   | IF SAWs for Analog Cellular Communications        | 223  |

| Section 8:   | IF SAWs for Digital European Cordless             |      |

|              | Telecommunications (DECT)                         | 229  |

| Section 9:   | IF SAWs for Personal Communications Systems (PCS) | 241  |

| Section 10:  | IF SAWs for Wireless Local Area Networks (WLAN)   | 247  |

| Section 11:  | Application Notes                                 | 253  |

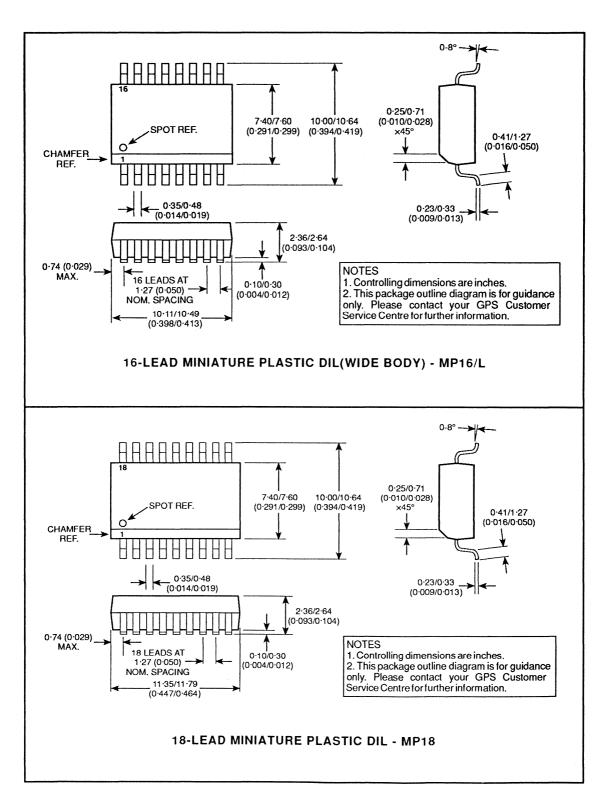

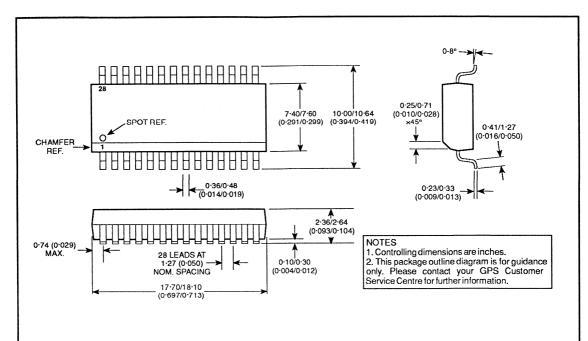

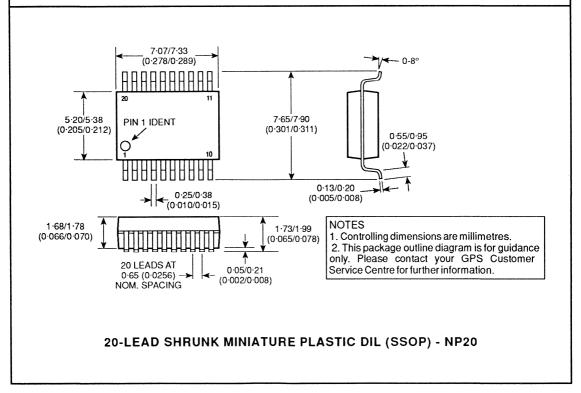

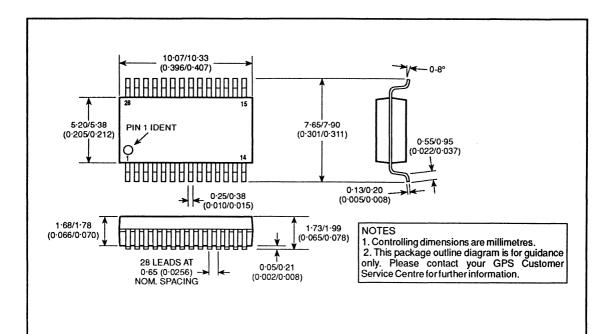

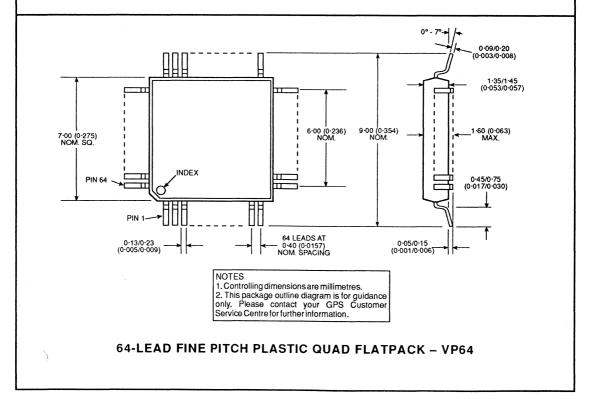

| Section 12:  | Package Outlines                                  | 287  |

| Section 13:  | GPS Locations                                     | 299  |

# Product List - by circuit type PLLs (Phased Lock Loop)

| Type No. | Description                                                                           | Page |

|----------|---------------------------------------------------------------------------------------|------|

| NJ88C33  | Frequency synthesiser (I <sup>2</sup> C bus programmable) with current source outputs | 11   |

| NJ88C50  | Dual low power frequency synthesiser                                                  | 21   |

## Prescalers

| Type No. | Description                                    | Page |

|----------|------------------------------------------------|------|

| SP8713   | 1100MHz very low current three modulus divider | 37   |

| SP8714   | 2100MHz very low current multi-modulus divider | 44   |

| SP8715   | 1100MHz very low current multi-modulus divider | 51   |

# Paging Receivers & Decoders

| Type No. | Description                                | Page |

|----------|--------------------------------------------|------|

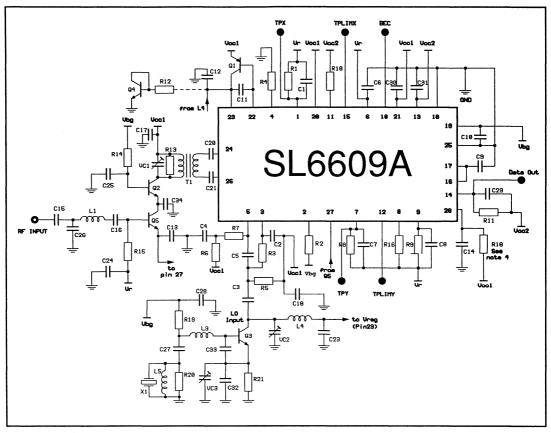

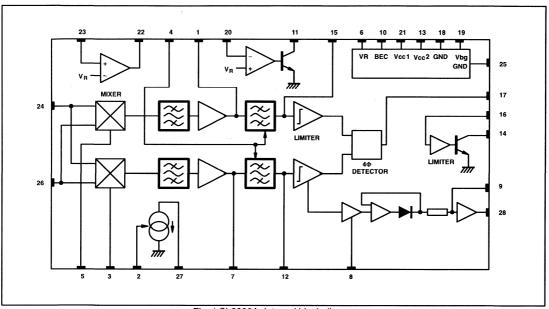

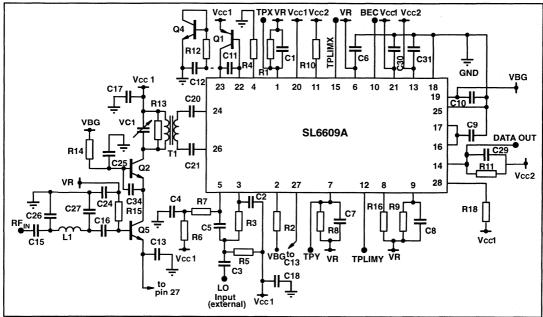

| SL6609A  | Direct conversion FSK data receiver        | 61   |

| SL6610   | Direct conversion FSK data receiver        | 77   |

| SL6619   | 450MHz direct conversion receiver with AFC | 94   |

| SL6649-1 | 200MHz direct conversion FSK data receiver | 95   |

## **Analog Cellular Components**

| Type No. | Description                                       | Page |

|----------|---------------------------------------------------|------|

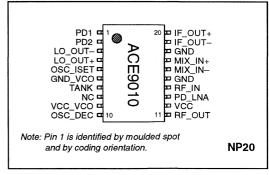

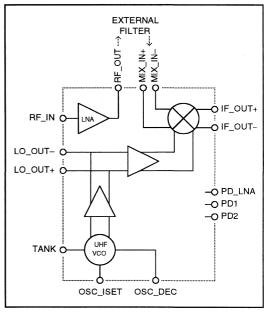

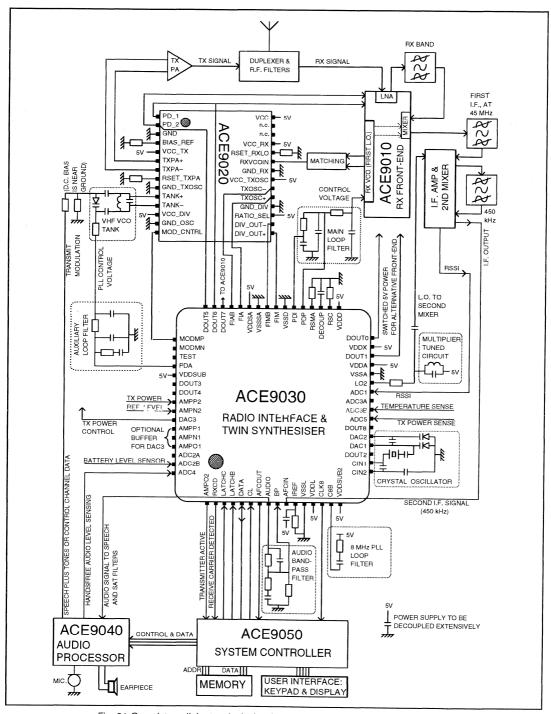

| ACE9010  | RF Front End with VCO                             | 109  |

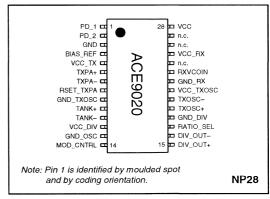

| ACE9020  | Receiver and Transmitter Interface                | 111  |

| ACE9030  | Radio Interface and Twin Synthesiser              | 115  |

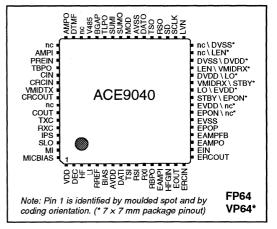

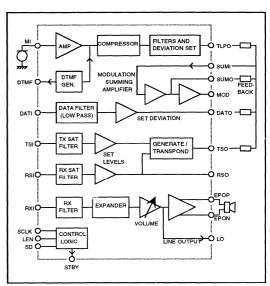

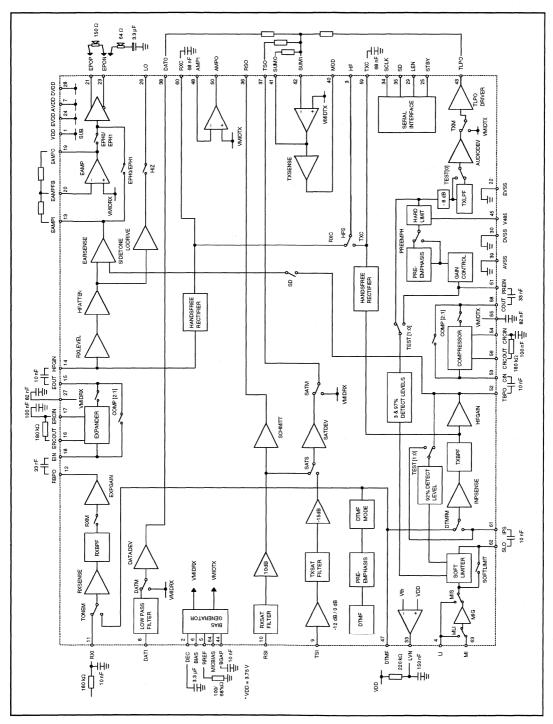

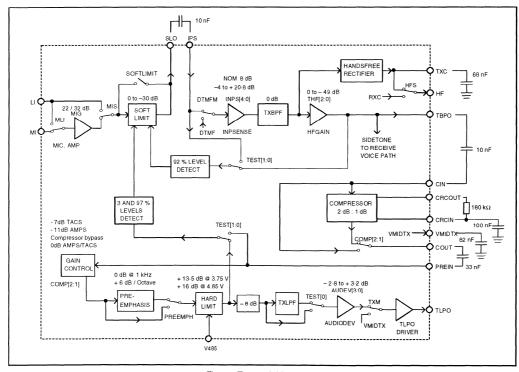

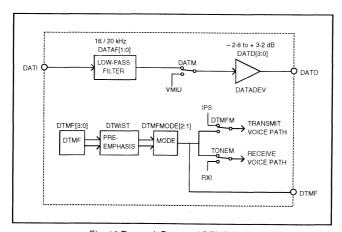

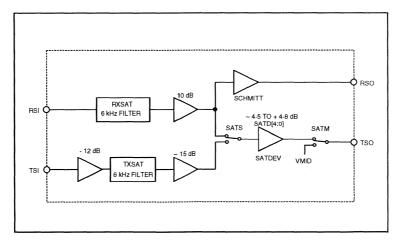

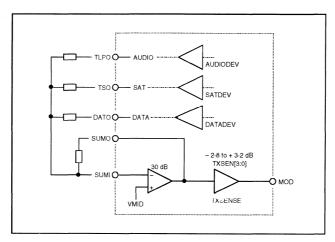

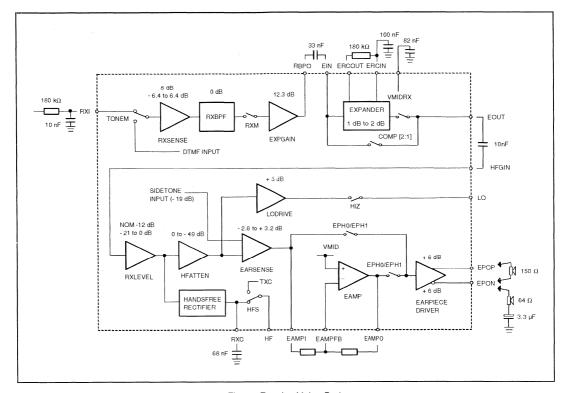

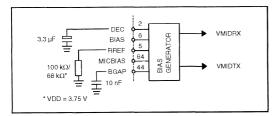

| ACE9040  | Audio Processor for AMPS and TACS cellular phones | 151  |

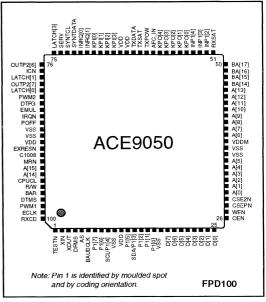

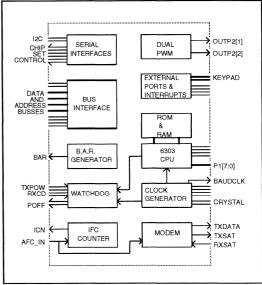

| ACE9050  | System Controller and Data Modem                  | 181  |

### **PCM Circuits**

| Type No. | Description                                 | Page |

|----------|---------------------------------------------|------|

| MV1442   | HDB3 Encoder/decoder/clock register         | 189  |

| MV1449   | 8.5MBit PCM Signalling Circuit/HDB3 encoder | 197  |

| MV1471   | HDB3/AMI Encoder/decoder                    | 206  |

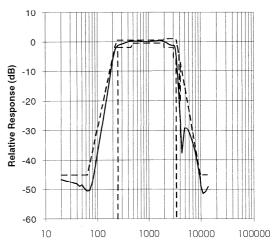

# IF SAWs for GSM Digital Cellular Communications

| Type No. | Description                       | Page |

|----------|-----------------------------------|------|

| DW9241   | 78.8125MHz Low loss IF SAW filter | 215  |

| DW9256   | 133MHz IF SAW filter              | 217  |

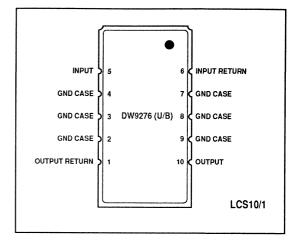

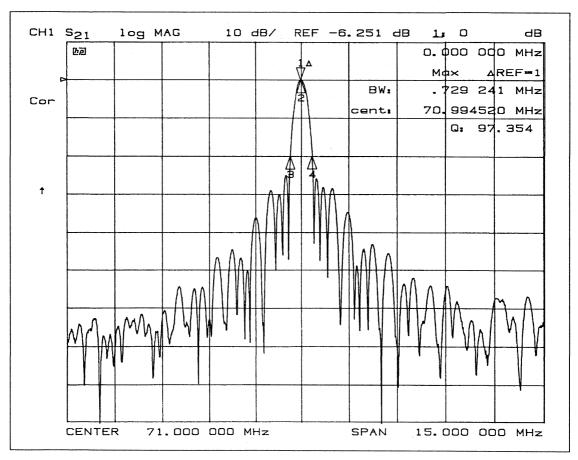

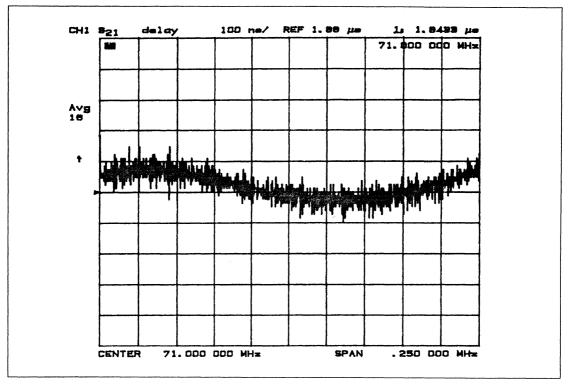

| DW9276   | 71MHz IF SAW filter               | 220  |

# IF SAWs for Analog Cellular Communications

# IF SAWs for Digital European Cordless Telecommunications (DECT)

| Type No. | Description              | Page |

|----------|--------------------------|------|

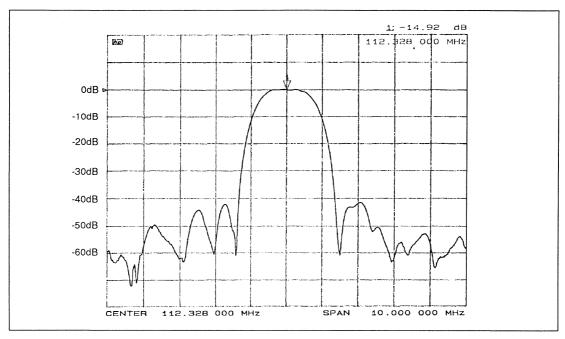

| DW9249   | 112.32MHz IF SAW filter  | 231  |

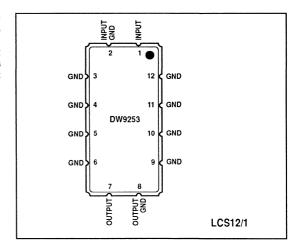

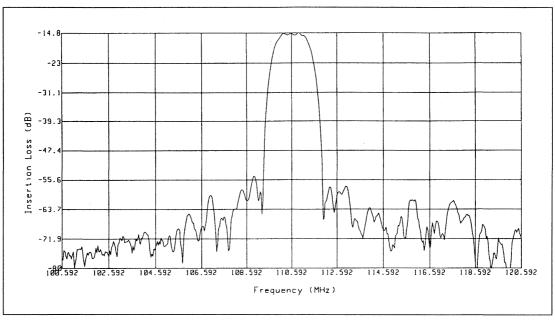

| DW9253   | 110.592MHz IF SAW filter | 233  |

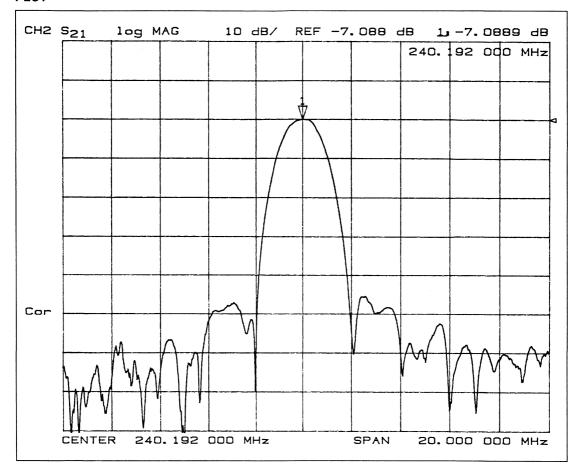

| DW9268   | 240.192MHz IF SAW filter | 235  |

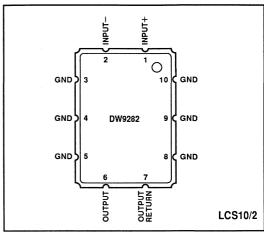

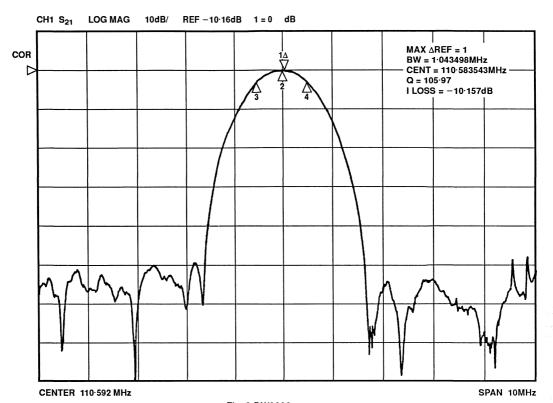

| DW9282   | 110.592MHz IF SAW filter | 238  |

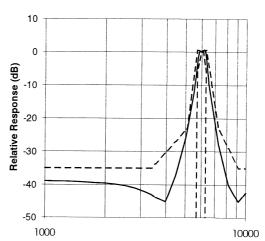

# IF SAWs for Personal Communications Systems (PCS)

| Type No. | Description             | Page |

|----------|-------------------------|------|

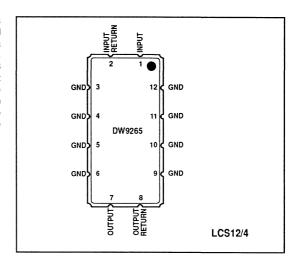

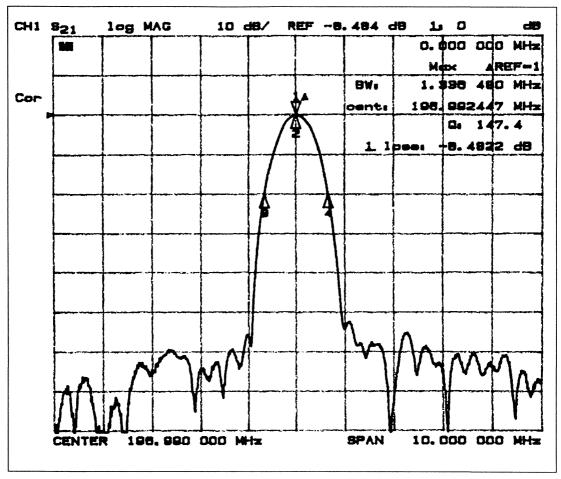

| DW9265   | 196.99MHz IF SAW filter | 243  |

# IF SAWs for Wireless Local Area Networks (WLAN)

# Product List - alpha numeric

| Type No. | Description                                                                                          | Page |

|----------|------------------------------------------------------------------------------------------------------|------|

| ACE9010  | RF Front End with VCO                                                                                | 109  |

| ACE9020  | Receiver and Transmitter Interface                                                                   | 111  |

| ACE9030  | Radio Interface and Twin Synthesiser                                                                 | 115  |

| ACE9040  | Audio Processor for AMPS and TACS cellular phones                                                    | 151  |

| ACE9050  | System Controller and Data Modem                                                                     | 181  |

| DW9241   | 78.8125MHz Low loss IF SAW Filter                                                                    | 215  |

| DW9249   | 112.32MHz IF SAW Filter                                                                              | 231  |

| DW9253   | 110.592MHz IF SAW Filter                                                                             | 233  |

| DW9256   | 133MHz IF SAW Filter                                                                                 | 217  |

| DW9265   | 196.99MHz IF SAW Filter                                                                              | 243  |

| DW9268   | 240.192MHz IF SAW Filter                                                                             | 235  |

| DW9270   | 240MHz IF SAW Filter                                                                                 | 249  |

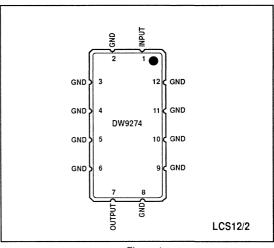

| DW9274   | 92.025MHz IF SAW Filter                                                                              | 225  |

| DW9276   | 71MHz IF SAW Filter                                                                                  | 220  |

| DW9282   | 110.592MHz IF SAW Filter                                                                             | 238  |

| MV1442   | HDB3 Encoder/decoder/clock register                                                                  | 189  |

| MV1449   | 8.5MBit PCM Signalling circuit/HDB3 encoder                                                          | 197  |

| MV1471   | HDB3/AMI Encoder/decoder                                                                             | 206  |

| NJ88C33  | Frequency synthesiser (I <sup>2</sup> C bus programmable) with current source phase detector outputs | 11   |

| NJ88C50  | Dual low power frequency synthesiser                                                                 | 21   |

| SL6609A  | Direct conversion FSK data receiver                                                                  | 61   |

| SL6610   | Direct conversion FSK data receiver                                                                  | 77   |

| SL6619   | 450MHz direct conversion receiver with AFC                                                           | 94   |

| SL6649-1 | 200MHz direct conversion FSK data receiver                                                           | 95   |

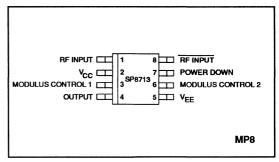

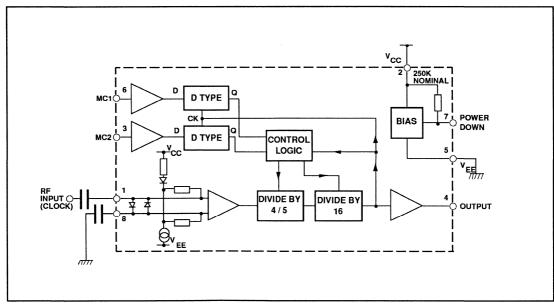

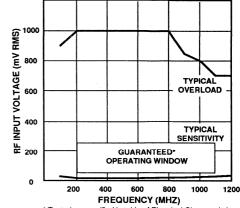

| SP8713   | 1100MHz very low current three modulus divider                                                       | 37   |

| SP8714   | 2100MHz very low current multi-modulus divider                                                       | . 44 |

| SP8715   | 1100MHz very low current multi-modulus divider                                                       | 51   |

|          |                                                                                                      |      |

# Section 1 PLLs (Phased Lock Loop)

# FREQUENCY SYNTHESISER (I<sup>2</sup>C BUS PROGRAMMABLE) WITH CURRENT SOURCE PHASE DETECTOR OUTPUTS

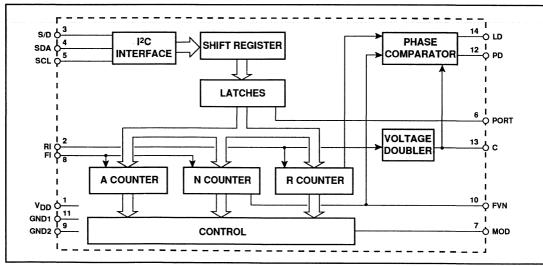

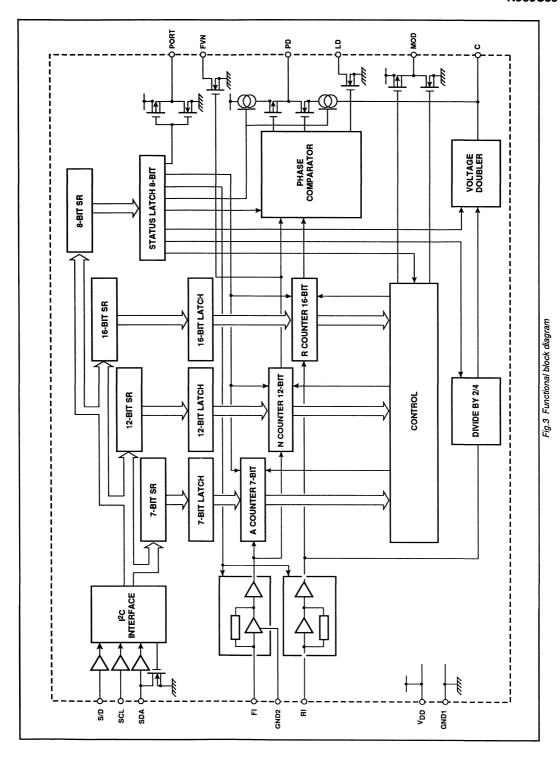

The NJ88C33 is a synthesiser circuit fabricated on GPS's 1.4 micron CMOS process, assuring very high performance. It is I<sup>2</sup>C compatible and can also be programmed at up to 5MHz. It contains a 16-bit R counter, a 12-bit N counter and a 7-bit A counter.

A digital phase comparator gives improved loop stability with current source outputs to reduce loop components. A voltage doubler is provided for the loop driver to improve control voltage range to the VCO when operating at low supply voltages.

#### **FEATURES**

- Easy to Use

- Low Power Consumption (15mW)

- Single Supply 2.5V to 5.5V

- Digital Phase Comparator with Current Source Outputs

- Serial (I<sup>2</sup>C Compatible) Programming, 5MHz max

- Channel Loading in 8µs

- 150MHz Input Frequency Without Prescaler at 4.5V (52MHz at 2.7V)

- Standby Modes

- Use of Two-Modulus Prescaler is Possible

#### **APPLICATIONS**

- Cordless Telephones (CT2, DECT)

- Cellular Telephones (GSM, PCN, ETACS)

- Hand Held Marine Radios

- Sonarbuoys

- Video Clock generators

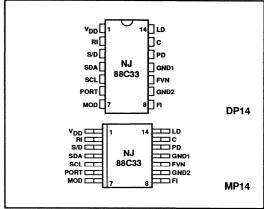

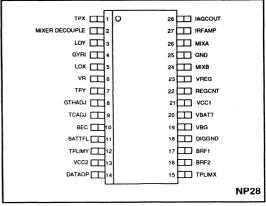

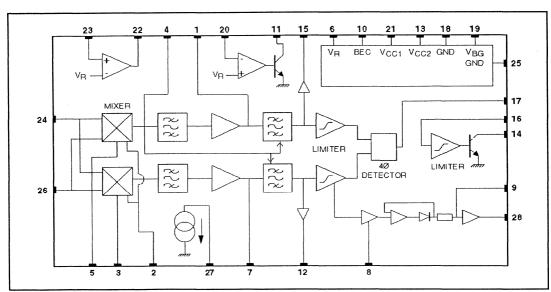

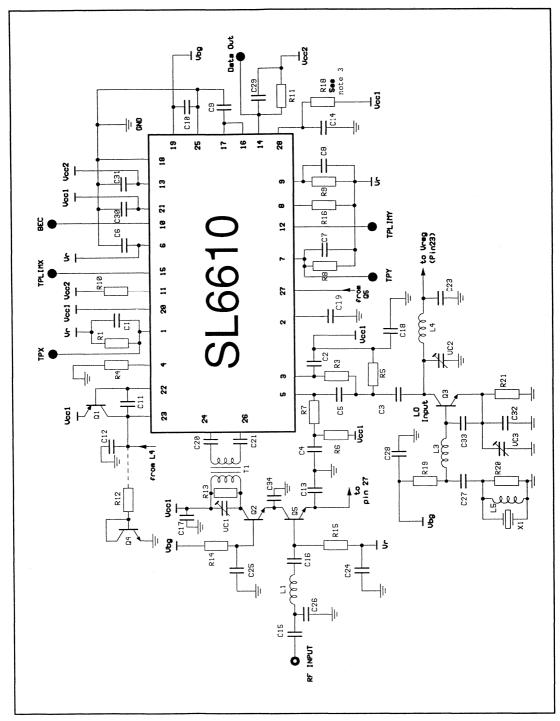

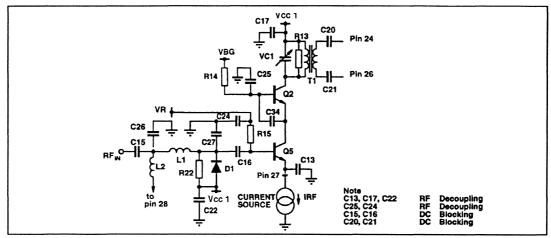

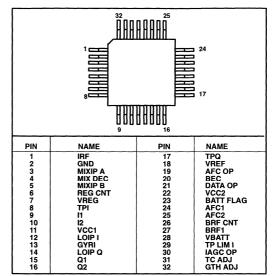

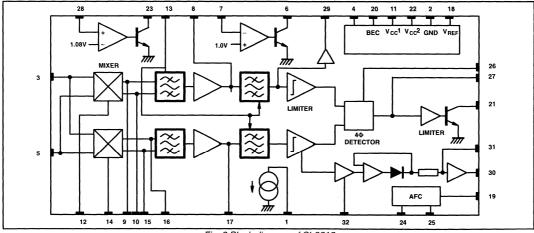

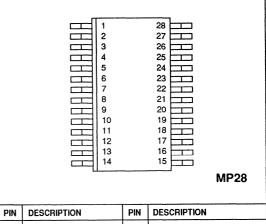

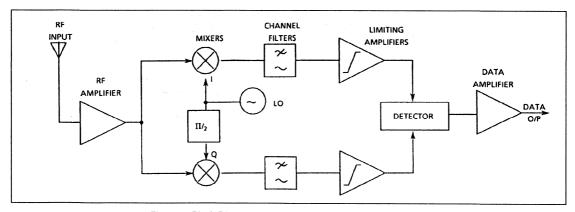

Fig.1 Pin connections (not to scale) - top views

#### ABSOLUTE MAXIMUM RATINGS

Supply voltage,  $V_{DD}$  -0.3V to 7V Input voltage,  $V_{IM1}$  -0.3 to  $V_{DD}$  +0.3V Output voltage on pin 13,  $V_{IM2}$  - $V_{DD}$  to 0V Storage temperature,  $T_{eln}$  -55°C to +125°C

#### ORDERING INFORMATION

NJ88C33 MA DP (Industrial - Plastic DIL package)

NJ88C33 MA MP (Industrial - Miniature Plastic DIL package)

Fig.2 Simplified block diagram of NJ88C33

#### **PIN DESIGNATIONS**

| Pin<br>No. | Pin<br>Name     | Description                                                                                                                                                                                                                                                                                                                                 |

|------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | V <sub>DD</sub> | Supply voltage (normally 5V or 3V).                                                                                                                                                                                                                                                                                                         |

| 2          | RI              | Reference frequency input from an accurate source, normally a crystal oscillator. The input is normally an AC coupled sinewave but may be a DC coupled square wave.                                                                                                                                                                         |

| 3          | S/D             | Single/dual modulus operating mode selection input. Single modulus operation is selected by driving the pin low. 'High' selects dual modulus mode.                                                                                                                                                                                          |

| 4          | SDA             | I <sup>2</sup> C bus data input pin. It is also an open-drain output for generating I <sup>2</sup> C bus acknowledge pulses.                                                                                                                                                                                                                |

| 5          | SCL             | I <sup>2</sup> C bus clock input. It can be clocked at up to 5MHz.                                                                                                                                                                                                                                                                          |

| 6          | PORT            | Output control pin, which can be programmed via the I <sup>2</sup> C bus. It can be connected to the S/D pin to select single or dual modulus mode under bus control.                                                                                                                                                                       |

| 7          | MOD             | Modulus control pin. It is high in single modulus mode but switches in dual modulus operation. In dual modulus mode, MOD remains low during operation of the A counter until A=0; MOD then remains high until N=0, when both counters are reloaded. It can be programmed via the I <sup>2</sup> C bus as an open-drain or push-pull output. |

| . 8        | FI              | Frequency input from a VCO or prescaler. The input is normally an AC coupled sinewave but may be a DC coupled square wave.                                                                                                                                                                                                                  |

| 9          | GND2            | Dedicated ground for the FI input buffer. It should be connected to the VCO ground or the prescaler ground, if used. Any noise on this pin will affect the performance of the VCO loop.                                                                                                                                                     |

| 10         | FVN             | Open-drain output from the N counter.                                                                                                                                                                                                                                                                                                       |

| 11         | GND1            | Ground supply pin (global).                                                                                                                                                                                                                                                                                                                 |

| 12         | PD              | Tristate current output from the phase detector. The polarity of the output can be programmed via the I <sup>2</sup> C bus.                                                                                                                                                                                                                 |

| 13         | С               | Voltage doubler output. The operation of the doubler can be controlled via the I2C bus. In applications where the voltage doubler is switched off, this pin should be connected to GND1; a reservior capacitor should be connected from this pin to GND1 for applications where it is switched on.                                          |

| 14         | LD              | Open-drain lock detect output - requires integration if used.                                                                                                                                                                                                                                                                               |

### **OPERATING RANGE**

### Test conditions (unless otherwise stated):

PLL locked, RI = 10MHz

| Characteristic                                    | Symbol                              |            | Value | 1          | Unit    | Conditions                                                                                                                |

|---------------------------------------------------|-------------------------------------|------------|-------|------------|---------|---------------------------------------------------------------------------------------------------------------------------|

| Characteristic                                    | Symbol                              | Min.       | Тур.  | Max.       | Ollik   | Conditions                                                                                                                |

| Supply voltage Ambient temperature Supply current | V <sub>DD</sub><br>T <sub>amb</sub> | 2.5<br>-40 | 5     | 5.5<br>+85 | .c<br>∧ |                                                                                                                           |

| Single modulus                                    | I <sub>DD</sub>                     |            | 2.1   | 3.0        | mA      | FI = 50MHz, $V_{FI}$ = 150mVrms, N,R > 1000 without voltage doubler, $V_{DD}$ = 5V, $T_{amb}$ = 25°C                      |

| Dual modulus                                      | I <sub>DD</sub>                     |            | 2     | 3.0        | mA      | FI = 10MHz, V <sub>FI</sub> = 500mVrms, N,R > 1000 without voltage doubler, V <sub>DD</sub> = 5V, T <sub>amb</sub> = 25°C |

| Standby mode                                      | I <sub>DD</sub>                     |            |       | 1          | μА      | FI = 50MHz, V <sub>FI</sub> = 150mVrms, preamp off, divider off, V <sub>DD</sub> = 5V, T <sub>amb</sub> = 25°C            |

| Standby mode                                      | l <sub>DD</sub>                     |            | 1.0   | 1.5        | mA      | FI = 50MHz, V <sub>FI</sub> = 150mVrms, preamp on, divider off, V <sub>DD</sub> = 5V, T <sub>amb</sub> = 25°C             |

#### **ELECTRICAL CHARACTERISTICS**

These characteristics are guaranteed over the following conditions (unless otherwise stated):

$V_{DD} = 4.5V$  to 5.5V,  $T_{amb} = -40$ °C to +85°C INPUT SIGNALS

| Characteristic                                                                                                  | Symbol                                                          |                         | Value |                                             | Unit                  | Conditions                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------|-------|---------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Characteristic                                                                                                  | Symbol                                                          | Min.                    | Тур.  | Max.                                        | Olik                  | Conditions                                                                                                                    |

| Input Signals SDA,<br>SCL, S/D<br>Input voltage high<br>Input voltage low<br>Input capacitance<br>Input current | >                                                               | 0.7V <sub>DD</sub><br>0 |       | V <sub>DD</sub><br>0.3V <sub>DD</sub><br>10 | V<br>V<br>pF<br>μA    | V <sub>IN</sub> = V <sub>DD</sub> = 5.5V                                                                                      |

| Input signal RI<br>Input frequency<br>Input voltage<br>Input capacitance<br>Input current                       | f <sub>max</sub><br>V <sub>Irms</sub><br>C <sub>I</sub>         | 100                     |       | 52<br>10<br>10                              | MHz<br>mV<br>pF<br>μA | Sinewave input<br>Note 1, 2<br>V <sub>IN</sub> = V <sub>DD</sub> = 5.5V                                                       |

| Input signal FI<br>Input frequency<br>Input voltage<br>Input capacitance<br>Input current                       | f <sub>max</sub><br>V <sub>Irms</sub><br>C <sub>I</sub>         | 50                      |       | 52<br>10<br>10                              | MHz<br>mV<br>pF<br>μA | Dual modulus operation Sinewave input Note 1, 2 $V_{\text{IN}} = V_{\text{DD}} = 5.5 \text{V}$                                |

| Input signal FI<br>Input frequency<br>Input voltage                                                             | f <sub>max</sub><br>V <sub>Irms</sub><br>V <sub>Irms</sub><br>V | 30<br>100<br>200        |       | 150                                         | MHz<br>mV<br>mV<br>mV | Single modulus operation<br>Sinewave input<br>FI = 0-70MHz Note 1, 2<br>FI = 70-120MHz Note 1, 2<br>FI = 120-150MHz Note 1, 2 |

| Input capacitance<br>Input current                                                                              | C <sub>I</sub> I <sub>IN</sub>                                  |                         |       | 10<br>10                                    | pF<br>μA              | $V_{\rm IN} = V_{\rm DD} = 5.5 V$                                                                                             |

Note.1 Lowest noise floor achieved at 10dB above this level with I<sup>2</sup>C bus operating. The source impedance should be less than  $2k\Omega$ .

Note.2 DC coupled input amplitude  $V_{IRMS} > 0.8 V_{DD}$ .

#### OUTPUT SIGNALS

|                                                                          | Combat                             |                                | Value                                |                                  | 11-14                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------|------------------------------------|--------------------------------|--------------------------------------|----------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Characteristic                                                           | Symbol                             | Min.                           | Тур.                                 | Max.                             | Unit                 | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Output Signals SDA, LD<br>Output voltage low                             | V <sub>oL</sub>                    |                                |                                      | 0.4                              | ٧                    | Open drain, I <sub>OL</sub> = 3mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

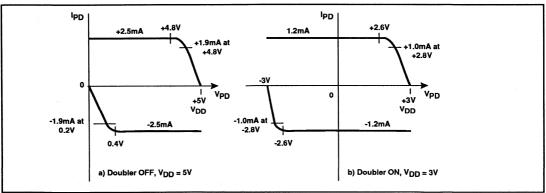

| Output Signal PD High current mode (see Fig.4) Low current mode Tristate | HU<br>HD<br>LU<br>LU<br>LD<br>Z    | 1.9<br>-1.9<br>0.475<br>-0.475 | 2.5<br>-2.5<br>0.625<br>-0.625<br>50 | 3.1<br>-3.1<br>0.775<br>-0.775   | mA<br>mA<br>mA<br>mA | $ \begin{array}{l} C_L = 400 \text{pF, tristate output} \\ 0 < V_{PD} < 4.5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 0.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 0 < V_{PD} < 4.6, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 0.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}\text{C Note 1} \\ 1.4 < V_{PD} < 5, \ V_{DD} = 5 \text{V, T} = 25^{\circ}C $ |

| Output Signal FVN<br>Output voltage low<br>Output low pulse width        | V <sub>OL</sub>                    |                                |                                      | 0.4<br>1/Fl                      | V                    | Open drain output $I_{OL} = 1 mA$ $C_{L} = 30 pF$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Output Signals MOD, PORT<br>Output voltage high<br>Output voltage low    | V <sub>OH</sub>                    | V <sub>DD</sub> -0.4           |                                      | 0.4                              | V                    | Push-pull output<br>IOH = 0.5mA<br>I <sub>OL</sub> = 0.5mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Output Signal LD Output voltage low Output low pulse width               | V <sub>OL</sub><br>t <sub>wL</sub> |                                | 10                                   | 0.4<br>1/FVN<br>1/f <sub>c</sub> | V<br>ns              | Open drain output  I <sub>OL</sub> = 3mA, C <sub>L</sub> = 30pF  Loop locked  Loop not locked  FVN = FI/N  f <sub>C</sub> = RI/R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Note.1 Temperature coefficient for current is typically -0.7%/°C

Fig. 4 Typical output signal PD, high current mode

| <b>VOLTAGE</b> | DOUBLER | V <sub>22</sub> ≤ 3V |

|----------------|---------|----------------------|

| Characteristic                 | Symbol         |                  | Value | •                                                  | Unit     | Conditions                                                                                       |

|--------------------------------|----------------|------------------|-------|----------------------------------------------------|----------|--------------------------------------------------------------------------------------------------|

| Characteristic                 | Symbol         | Min.             | Тур.  | Max.                                               | Onn      | Conditions                                                                                       |

| Output Pin C<br>Output voltage | V <sub>c</sub> | -V <sub>DD</sub> |       | -V <sub>DD</sub> + 0.8V<br>-V <sub>DD</sub> + 1.5V | <b>V</b> | $f_{VD} = 2MHz, I_{OC} = 0\mu A, V_{DD} = 3V$<br>$f_{VD} = 2MHz, I_{OC} = 100\mu A, V_{DD} = 3V$ |

| Current Consumption            | I <sub>D</sub> |                  |       | 100                                                | μΑ       | $f_{VD} = 2MHz, I_{OC} = 0\mu A, V_{DD} = 3V$                                                    |

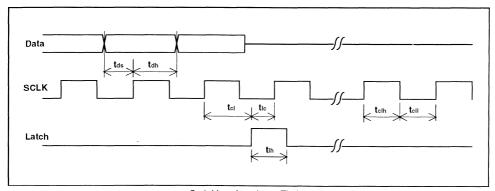

#### **TIMING INFORMATION**

| Characteristic                                                                | Symbol                                                                   |             | Value |                         | Unit                           | Conditions                                                                                                                                                                             |  |  |  |  |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------|-------|-------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Characteristic                                                                | Symbol                                                                   | Min.        | Тур.  | Max.                    | Onn                            | Conditions                                                                                                                                                                             |  |  |  |  |

| Input Signal RI Input frequency Input frequency Rise time Fall time Slew rate | f max<br>f max<br>t R<br>t F                                             | 0 0         |       | 52<br>10<br>1.5<br>1.5  | MHz<br>MHz<br>μs<br>μs<br>V/μs | V <sub>DD</sub> = 2.7V                                                                                                                                                                 |  |  |  |  |

| Input Signal FI Input frequency Input frequency Rise time Fall time Slew rate | f max<br>f max<br>t R<br>t F                                             | 0<br>0<br>3 |       | 52<br>20<br>1.5<br>1.5  | MHz<br>MHz<br>μs<br>μs<br>V/μs | Dual modulus $V_{DD} = 2.7V$                                                                                                                                                           |  |  |  |  |

| Input Signal FI Input frequency Input frequency Rise time Fall time Slew rate | f max<br>f max<br>t R<br>t F                                             | 0<br>0<br>3 |       | 150<br>52<br>1.5<br>1.5 | MHz<br>MHz<br>μs<br>μs<br>V/μs | Single modulus $V_{DD} = 2.7V$                                                                                                                                                         |  |  |  |  |

| Output Signal PORT Rise time Fall time                                        | t <sub>R</sub><br>t <sub>F</sub>                                         |             |       | 1 1                     | μs<br>μs                       | C <sub>L</sub> = 30pF<br>C <sub>L</sub> = 30pF                                                                                                                                         |  |  |  |  |

| Output Signal FVN<br>Fall time                                                | t <sub>F</sub>                                                           |             | 20    |                         | ns                             | C <sub>L</sub> = 30pF                                                                                                                                                                  |  |  |  |  |

| Output Signal MOD Rise time Fall time Delay time (L→H) Delay time (H→L)       | t <sub>R</sub><br>t <sub>F</sub><br>t <sub>DLH</sub><br>t <sub>DHL</sub> | :           |       | 10<br>10<br>15<br>15    | ns<br>ns<br>ns<br>ns           | $\begin{array}{c} C_L = 30 pF \\ C_L = 30 pF \\ C_L = 30 pF \end{array}$<br>C <sub>L</sub> = 30 pF Measured from +Ve edge of FI<br>C <sub>L</sub> = 30 pF Measured from +Ve edge of FI |  |  |  |  |

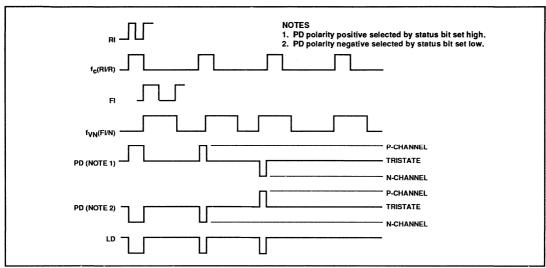

#### PHASE COMPARATOR

The phase comparator produces current pulses of duration equal to the difference in phase between the comparison frequency (fc=RI/R), and  $f_{VN}$ , the divided-down VCO frequency (FI/N).

When status bit 4 is set high the positive polarity mode of the output PD is selected. When fc leads  $f_{vN}$  the PD output goes high; when  $f_{vN}$  leads fc it goes low. Similarly, selecting the negative polarity mode of PD by programming bit 4 of the status register low causes PD to have the inverse polarity. The loop filter integrates the current pulses to produce a voltage drive to the VCO.

No pulses are produced when locked. The lock detect output, LD, produces a logic '0' pulse equal to the phase difference between  $f_c$  and  $f_{v_N}$ .

When the phase difference between fc and  $f_{vN}$  is too small to be resolved by the phase detector then no current pulses are produced. In this region the loop does not reduce the close-in noise on the VCO output. This can be overcome using a very high value resistor to leak a few nanoAmps of current from the filter and keep the loop on the edge of the region.

Fig. 5 Phase comparator phase diagram

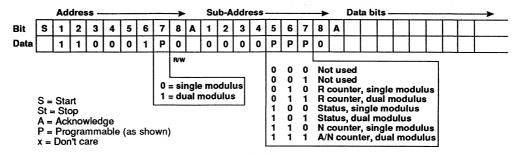

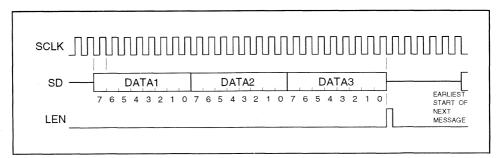

#### **PROGRAMMING**

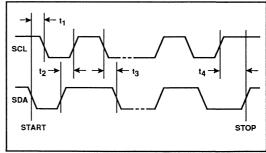

#### Transmission Protocol

IPC programming messages consist of an address byte followed by a sub-address byte followed by 1, 2 or 3 bytes of data. Bit 7 of the address byte must match the setting of the S/D pin for the address to be recognised. This allows for separate addressing of two NJ88C33 synthesisers on the same bus. The sub-address should be set to select the correct registers to be programmed and should be followed by the appropriate number of data bytes. Registers are not programmed until the complete message protocol has been checked.

Each message should commence with a START condition and end with a STOP condition unless followed immediately by another transfer, when the STOP condition may be omitted.

Data is transferred from the shift register to the latches on a STOP condition or by a second START condition.

A START condition is indicated by a falling edge on the Serial Data line, SDA, when the Serial Clock line, SCL, is high.

A rising edge on SDA when SCL is high indicates a STOP condition as shown in Fig.6.

Data on SDA is clocked into the NJ88C33 on the rising edge of SCL. The NJ88C33 acknowledges each byte transferred to it by pulling the SDA line low for one cycle of SCL after the last bit has been received.

Fig. 6 PC timing diagram

#### 12C TIMING INFORMATION

VDD = 4.5V to 5.5V, Tamb = -40°C to +85°C

| Parameter               | Symbol           | Va   | lue  | Unit     |

|-------------------------|------------------|------|------|----------|

|                         | <b>-</b> ,       | Min. | Max. | <b>0</b> |

| Serial clock frequency  | f <sub>scl</sub> |      | 5    | MHz      |

| SCL hold after START    | t,               | 200  |      | ns       |

| Data set-up time        | t <sub>2</sub>   | 20   |      | ns       |

| Data hold after SCL low | t <sub>3</sub>   | 0    |      | ns       |

| SCL set-up before STOP  | t <sub>4</sub>   | 20   |      | ns       |

#### **Address and Sub-Address Formats**

The correct addressing sequence for the NJ88C33 is shown below. The START condition is followed by the address byte, the acknowledge from the NJ88C33, the sub-

address byte, another acknowledge then the associated data. The correct values for each address and sub-address are listed, together with the message selection options.

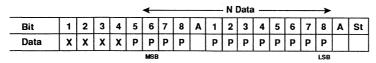

#### **Data Formats**

Each of the data formats should be preceded contiguously by the addressing sequence given above.

#### R counter: single or dual modulus

|      | Bit 1 2 3 4 5 6 7 8 A 1 2 3 4 5 6 7 |   |   |   |   |   |   |   |   |   |   |   |   |   |   | <b>→</b> |     |   |    |

|------|-------------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----------|-----|---|----|

| Bit  | 1                                   | 2 | 3 | 4 | 5 | 6 | 7 | 8 | À | 1 | 2 | 3 | 4 | 5 | 6 | 7        | 8   | A | St |

| Data | Р                                   | Р | Р | Р | Р | Р | Р | Р |   | Р | Р | Р | Р | P | Р | Р        | Р   |   |    |

|      | MSB                                 |   |   |   |   |   |   |   |   |   |   |   |   |   | • | •        | LSB |   |    |

#### Status: single or dual modulus

|      | Data | ۰ — |   |   |   |   |   | -> |   |    |

|------|------|-----|---|---|---|---|---|----|---|----|

| Bit  | 1    | 2   | 3 | 4 | 5 | 6 | 7 | 8  | Α | St |

| Data | Р    | Р   | Р | Р | Р | P | Р | Р  |   |    |

|                                      | Status By                                                                                                                                                                            | te                                                                                                                                 |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Bit                                  | 0                                                                                                                                                                                    | 1                                                                                                                                  |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | PORT = low<br>Counters off <sup>(1)</sup><br>FI and RI off <sup>(2)</sup><br>PD = polarity negative<br>PD bias = 0.625mA<br>f <sub>vD</sub> = RI/2<br>Doubler off<br>MOD = push-pull | PORT = high Counters on FI and RI on PD = polarity positive PD bias = 2.5mA f <sub>vo</sub> = RI/4 Doubler on (3) MOD = open drain |

#### **NOTES**

- 1. In this standby mode the counters are disabled but the voltage doubler and I<sup>2</sup>C interface can both function.

- In this standby mode the FI and RI preamplifiers are disabled, which stops the counters and the voltage doubler. The I<sup>2</sup>C interface still operates.

- 3. The voltage doubler should only be used when  $V_{DD} \le 3.0V$

#### N counter: single modulus

#### A/N counters : dual modulus

|      |     |   |   |   |   | <b>←</b> |   |   | A | Data | ۰ |   | <b>→</b> | <del></del> |   |   |   |   | N D | ata |   |   |   |   |   | <b>→</b> |          |    |

|------|-----|---|---|---|---|----------|---|---|---|------|---|---|----------|-------------|---|---|---|---|-----|-----|---|---|---|---|---|----------|----------|----|

| Bit  | 1   | 2 | 3 | 4 | 5 | 6        | 7 | 8 | Α | 1    | 2 | 3 | 4        | 5           | 6 | 7 | 8 | Α | 1   | 2   | 3 | 4 | 5 | 6 | 7 | 8        | Α        | St |

| Data | X   | x | X | х | P | Р        | Р | Р |   | Р    | Р | Р | Р        | P           | Р | Р | Р |   | Р   | Р   | Р | Р | Р | Р | Р | Р        |          |    |

|      | MSB |   |   |   |   |          |   |   |   |      | - |   | LSB      | MSB         |   |   |   | - |     |     |   |   |   |   |   | LSB      | <u> </u> |    |

#### **APPLICATION CIRCUITS**

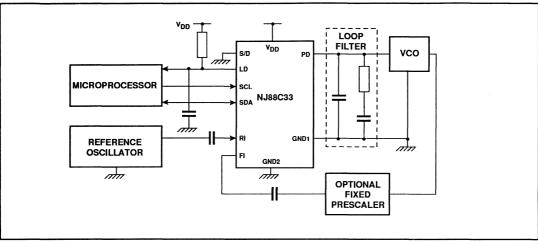

#### Single Modulus

In this mode, the NJ88C33 synthesiser can be used with or without a fixed modulus prescaler. The R counter is programmed with a value to produce a comparison frequency fc. When the N counter is changed by 1 the loop is no longer in lock and the phase detector output produces current pulses to bring the loop back into lock. These pulses are integrated by the loop filter to produce the VCO voltage drive. When the VCO loop is locked, FI/N=f<sub>c</sub> i.e., the VCO frequency is N x f<sub>c</sub>.

Using a prescaler with a division ratio P, the smallest VCO output frequency step is  $Pf_c$  and the VCO frequency is  $PNf_c$ .

If a low pass filter is connected to the lock detect output as shown and sampled by the microprocessor, the proximity of the synthesiser loop to lock can be evaluated.

The A counter is not used in this mode.

Fig. 7 Single modulus application

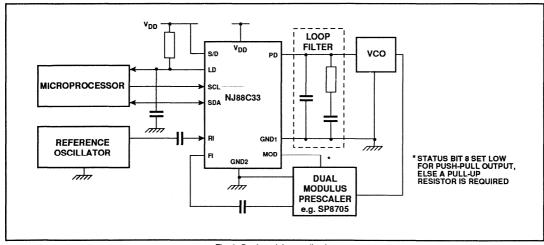

#### **Dual Modulus**

This mode allows much higher frequencies to be used in conjunction with a prescaler but maintains the step size, fc. In this mode, a dual modulus prescaler (with ratios P and P + 1) must be used with the NJ88C33. The A counter controls the MOD output, which is used to select the division ratio of the prescaler.

When the A counter is non-zero, the MOD output is low and goes high when the A counter has counted down to zero. MOD remains high until the N counter reaches zero, when both counters are re-loaded. Thus, the prescaler divides by P for N-A cycles and by P + 1 for A cycles of Fl. The VCO frequency is given by  $PNf_{_{\rm C}}+Af_{_{\rm C}}.$

Note that programming A = 0 produces a count of 128 cycles.

Fig. 8 Dual modulus application

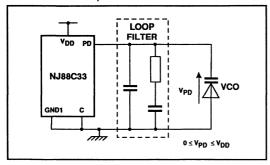

#### **VCO Driving Without Voltage Doubler**

To switch off the voltage doubler, bit 7 of the status register is programmed low. This will reduce current consumption and minimise noise. The voltage doubler output C should be connected to GND1 as connection to GND2 would induce noise in the VCO loop.

Fig. 9 Driving a VCO without voltage doubler

#### **Further Applications Information**

A stand-alone programmer card and an evaluation board are available for evaluating the NJ88C33. The programmer card allows two sets of variables to be programmed into both the divider and status registers during alternate programming cycles, at either the standard PC bus rate of 100kHz or at 2MHz.

Initialisation is with either a manual push-button or by an external logic level pulse; a synchronisation output is provided to allow a quick assessment of 'step' and 'settle' responses to be made.

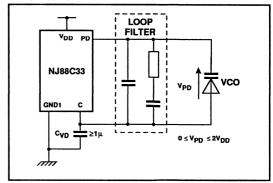

#### **VCO Driving With Voltage Doubler**

The voltage doubler is switched on by setting bit 7 of the status register high. It is recommended that a reservoir capacitor of at least 1µF be connected from C to GND1.

The voltage doubler is designed to boost VCO drive in low voltage applications.

Fig. 10 Driving a VCO using the voltage doubler

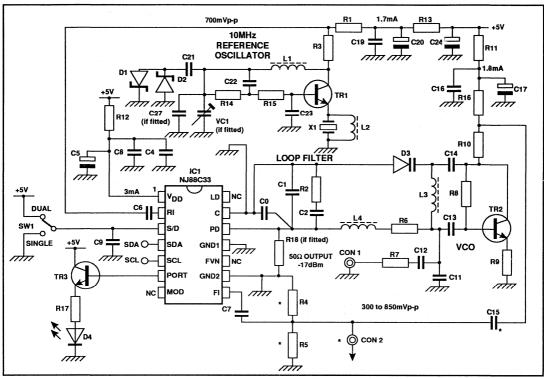

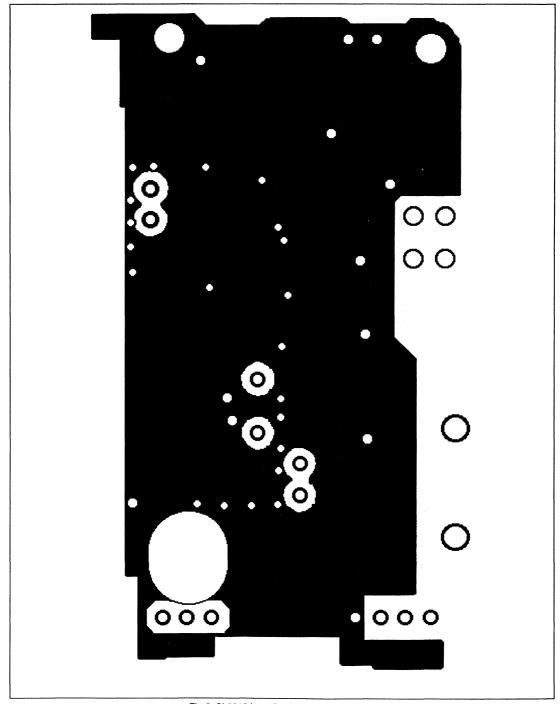

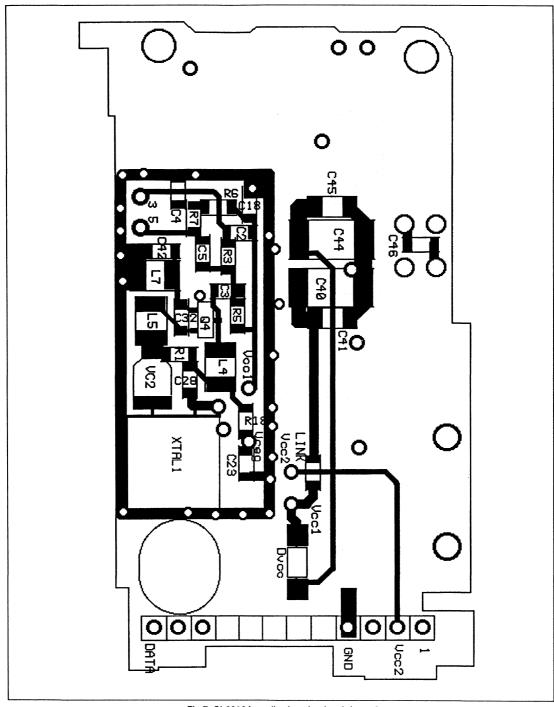

The NJ88C33 evaluation board (Fig. 11) dernonstrates the preferred layout technique - providing a reference oscillator, a 60 to 80MHz VCO and a simple loop filter to complete a minimal frequency synthesiser loop. The two units allow analysis of different loop variables as well as the selection of comparison frequencies for fast frequency-hopping loops.

Application Note: AN94, 'Using the NJ88C33 PLL Synthesiser' explains the design equations and demonstrates the use of the device, and is available from your local GPS customer service centre.

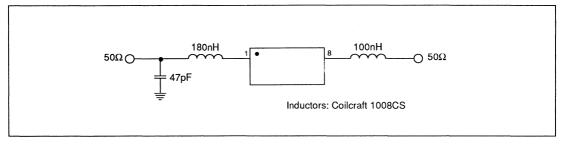

Fig. 11 Typical applications circuit

#### **COMPONENT LIST FOR FIG. 11**

|                                                                                              | Сар                                                                                                                                                                     | acito                                         | rs                                                                                                                                 | Re                         | sistors                                                                                                            | Inductors                                                                                                                                                          |                                         | Miscellaneous                                                                                    |

|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------|

| C0<br>C1<br>C2<br>C4<br>C5<br>C6<br>C7<br>C8<br>C9<br>C11<br>C12<br>C13<br>C14<br>C15<br>C16 | 1nF 10%<br>100nF 10%<br>1μF Tant.<br>10nF 10%<br>22μF/35V Elect.<br>10nF 10%<br>1nF 10%<br>1nF 10%<br>1nF 10%<br>150pF 5% NPO<br>1nF 10%<br>2p7 ± 0.5pF NPO<br>10nF 10% | C17<br>C19<br>C20<br>C21<br>C22<br>C23<br>C24 | 22μF/35V Elect.<br>10nF 10%<br>22μF/35V Elect.<br>10nF 10%<br>10nF 10%<br>22pF 5% NPO<br>22μF/35V Elect.<br>22pF 5% NPO<br>3p5-22p | R2<br>R3<br>R4<br>R5<br>R6 | 270Ω<br>470Ω<br>330Ω<br>100Ω<br>100Ω<br>1kΩ<br>120Ω<br>27kΩ<br>Link<br>10Ω<br>10Ω<br>22kΩ<br>2.7kΩ<br>330R<br>100Ω | 15μH 10% 220μH 10% 180nH 20% 470μH 10%  Diodes  1N6263 Schottky 1N6263 Schottky BBY40 varicap 5mm red LED  Transistors  BFS17 RF NPN BFS17 RF NPN 2N3904 Switching | IC1<br>X1<br>SW1<br>CON1<br>CON2<br>PCB | NJ88C33<br>10.00MHz 5ppm series<br>Miniature slide switch<br>SMC socket<br>SMC socket<br>C33ISS2 |

|                                                                                              |                                                                                                                                                                         | i                                             |                                                                                                                                    | R18                        | ззмΩ                                                                                                               | J                                                                                                                                                                  |                                         |                                                                                                  |

#### **NOTES**

- 1. With the exception of electrolytics, all capacitors are surface mount types.

- 2. All resistors are 0.25W, ±2%.

- 3. C0, C1, C2, C11, C12, C13 and C14 must be low leakage types.

- 4. R18 may be required to optimise VCO close in noise performance.

<sup>\*</sup> Insert C15, delete R4 and R5 if CON2 is to be used to monitor the VCO. Delete C15 insert R4 and R5 if CON is to provide an external source, otherwise short C15 and delete R4, R5 and CON2.

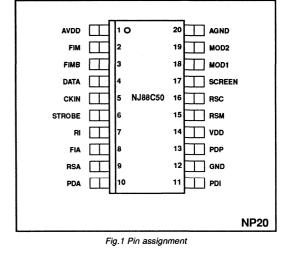

#### **DUAL LOW POWER FREQUENCY SYNTHESISER**

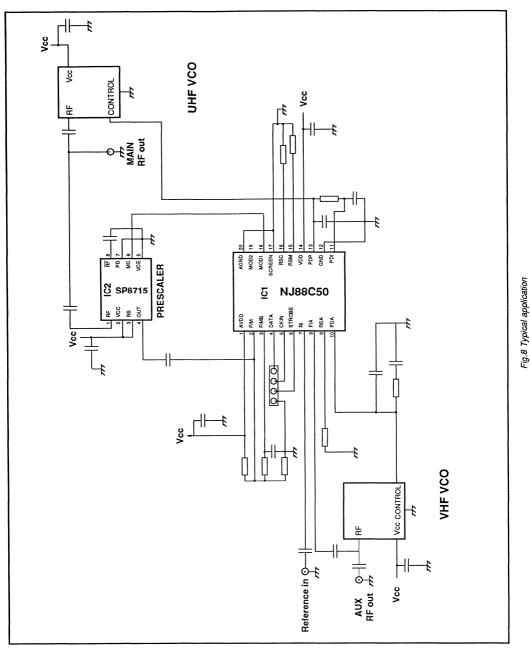

The NJ88C50 is a low power integrated circuit, designed as the heart of a fast locking PLL subsystem in a mobile radio application. It is manufactured on GEC Plessey Semiconductors 1.4 micron double polysilicon CMOS process, which ensures that low power and low noise performance is achieved. The device contains two synthesisers, one for the generation of VHF signals up to 125MHz and a second for UHF (when used with a mulitmodulus prescaler such as the SP8713/14/15). The main synthesiser has the capability of driving a dual speed loop filter and also can perform Fractional-N interpolation. Both synthesisers use current source outputs from their phase detectors to minimise external components. Various sections may be powered down for battery economy.

#### **FEATURES**

- 30MHz main synthesiser

- 125MHz auxiliary synthesiser

- Programmable output current from phase detector - up to 10mA

- High input sensitivity

- Fractional-Ninterpolator

- Supports up to 4 modulus prescalers

- SSOP package

#### **APPLICATIONS**

- NMT, AMPS, ETACS cellular

- GSM, IS-54, RCR-27 cellular

- DCS1800 microcellular

- DLMR, DSRR, TETRADECT, PHP cordless telephones

#### **ABSOLUTE MAXIMUM RATINGS**

#### ORDERING INFORMATION

NJ88C50\IG\NPAS - (Industrial temp range in SSOP package)

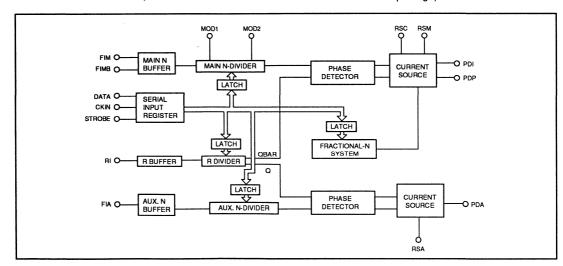

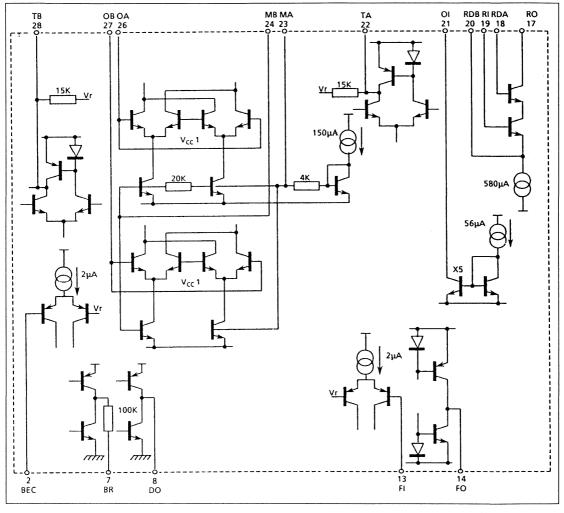

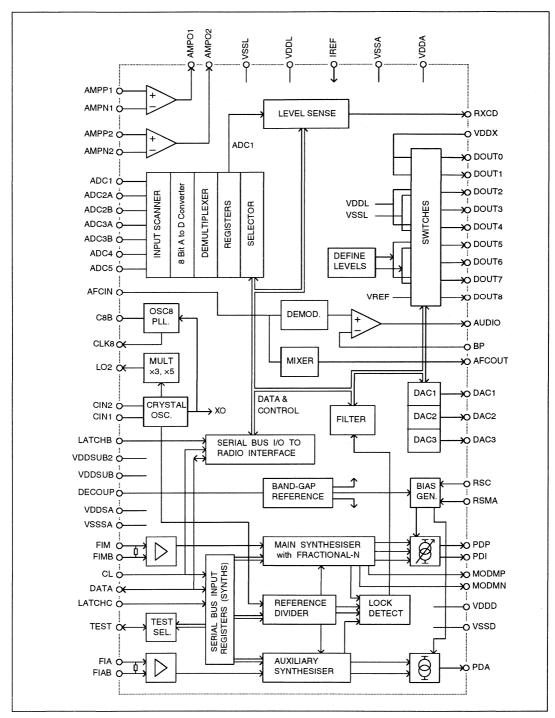

Fig.2 Simplified block diagram

#### **ARCHITECTURE**

Fig.2 shows a simplified block diagram of the NJ88C50, a more detailed description of each block and its function is given later in this datasheet.

The synthesiser consists of the following blocks

- 35MHz reference frequency input buffer

- 35MHz programmable reference divider

- 125MHz Auxiliary synthesiser input buffer

- 125MHz Auxiliary synthesiser programmable divider

- Auxiliary synthesiser phase detector with current source outputs

- 30MHz main synthesiser input buffer (differential inputs)

- 30MHz main synthesiser programmable divider and control logic

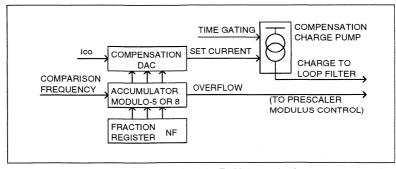

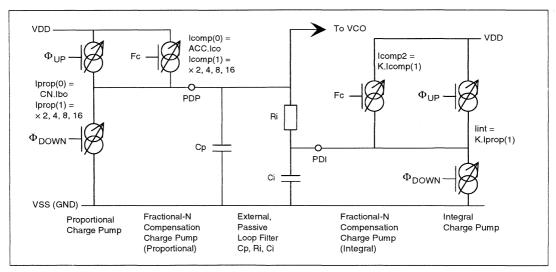

- Main synthesiser Fractional-N interpolation system

- Main synthesiser phase detector with dual current source outputs

#### **PIN DESCRIPTION**

| Pin | Name   | Function                                                                                                                                                    |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | AVDD   | Analog supply pin (nominally 5V).                                                                                                                           |

| 2   | FIM    | Main synthesiser balanced input buffer, may be used with single ended prescaler output if Fimb is biased.                                                   |

| 3   | FIMB   | Main synthesiser balanced input buffer, may be used with balanced prescaler output, or biased for single ended operation.                                   |

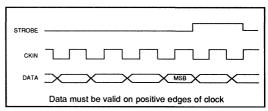

| 4   | DATA   | Serial input for programming data.                                                                                                                          |

| 5   | CKIN   | Serial clock input for programming bus.                                                                                                                     |

| 6   | STROBE | Program enable pin, active low.                                                                                                                             |

| 7   | RI     | Master reference frequency input, should be a.c coupled from an accurate source.                                                                            |

| 8   | FIA    | Auxiliary synthesiser frequency input, should be a.c coupled.                                                                                               |

| 9   | RSA    | Current setting resistor connection defining auxiliary phase detector output current.                                                                       |

| 10  | PDA    | Tristate current output from auxiliary phase detector.                                                                                                      |

| 11  | PDI    | Tristate current output from the main synthesiser's phase detector giving integral control.                                                                 |

| 12  | GND    | Digital ground supply pin.                                                                                                                                  |

| 13  | PDP    | Tristate current output from the main synthesiser's phase detector giving proportional control.                                                             |

| .14 | VDD    | Digital supply pin (nominally 5V).                                                                                                                          |

| 15  | RSM    | Current setting resistor connection defining main synthesiser's phase detector output currents.                                                             |

| 16  | RSC    | Current setting resistor connection defining the compensation current for fractional-N ripple elimination in the main synthesiser's current source outputs. |

| 17  | SCREEN | To be connected to ground to provide isolation of the modulus control pins from RF interference.                                                            |

| 18  | MOD1   | Modulus control pin (see truth table).                                                                                                                      |

| 19  | MOD2   | Modulus control pin (see truth table).                                                                                                                      |

| 20  | AGND   | Analog ground supply pin.                                                                                                                                   |

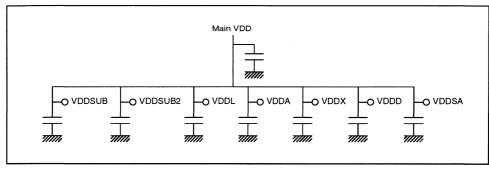

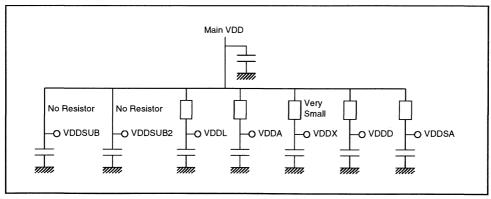

It is recommended that power supply pins are well decoupled to minimise power rail born interference.

#### **FUNCTIONAL DESCRIPTION**

The NJ88C50 has been designed using a modular concept, and its operation can be best summarised as these component blocks.

#### Reference divider

The reference divider is used to provide the reference signals needed for both the main and auxiliary synthesiser phase detectors. The divider allows for a twelve bit number to be loaded, via the serial bus, to select the required division ratio. Division ratios of 3 to 4095 can be used.

The reference divider input stage will accept a low level, AC coupled, sinewave input. It is anticipated that in most systems this will be provided by a stable reference source up to 35MHz, and so encompasses all the common TCXO (temperature controlled crystal oscillator) frequencies, such as 9.6, 12.8, 13.0, 19.44 and 26MHz.

A standby mode is supported so that the reference divider can be powered down, this is achieved using two of the serial program control bits.

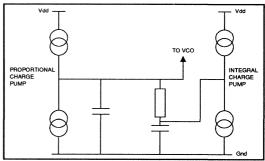

To reduce the possibility of unwanted interaction between the main and auxiliary synthesisers, the charge pumps do not take current at the same time. To achieve this the output of the reference divider has a duty factor of approximately 50:50, which then allows the Q and QBAR taps to be used for the auxiliary and main synthesisers respectively. By doing this the current pulses can be taken alternatively, minimising modulation of the power supply rails as current is drawn.

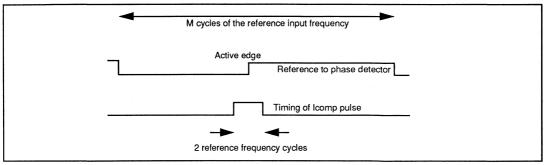

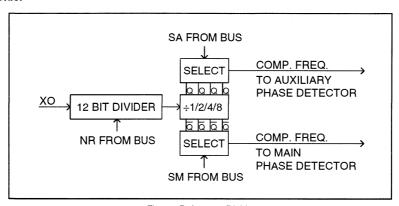

The reference divider consists of a 12 bit programmable divider followed by a 4 bit binary counter. This 4 bit counter gives a choice of divide by M, 2M, 4M or 8M.

A pair of programmable control bits are used to determine which of the divide by M, 2M, 4M or 8M outputs is supplied to the auxiliary synthesiser's phase detector and a further pair of control bits are used to determine which are supplied to the main synthesiser's phase detector.

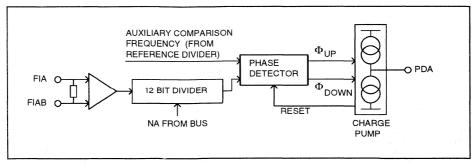

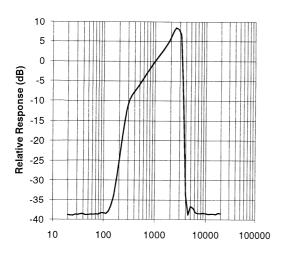

#### **Auxiliary synthesiser**

The auxiliary synthesiser operates over an input frequency range from 1 to 125MHz, without the use of an external prescaler. The synthesiser consists of a 12 bit N divider and a digital phase comparator with current source outputs. The reference frequency is supplied by the shared reference divider. Current source outputs allow a passive loop filter to be used.

When the auxiliary synthesiser is not in use, a standby mode is supported so that power consumption is reduced. This is achieved using one of the serial program control bits.

The divider is programmed with a 12 bit word allowing division ratios of 3 to 4095 to be used.

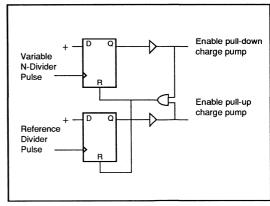

The auxiliary phase detector consists of the 2 D-type phase and frequency detector shown in Figure.3 below, the high and low outputs of which drive on-chip, opposing complementary charge pumps. This type of phase detector design eliminates non linearity or deadband around the zero phase error (locked) condition.

The charge pump output current level is set by an external resistor on the RSA pin (pin 9) up to a limit of  $250\mu A$  +/-10%. A pull up current pulse will indicate that the VCO frequency must be increased, whilst a pull down pulse indicates that the frequency must be decreased.

Fig.3 Auxiliary phase detector

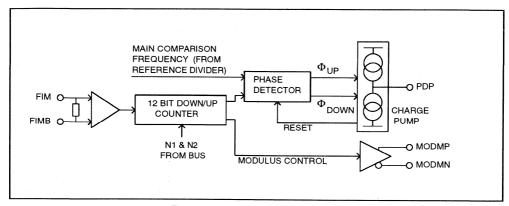

#### Main Synthesiser

The main synthesiser is capable of operating at frequencies up to 30MHz. The synthesiser uses the 12 bit reference divider, shared with the auxiliary synthesiser, a 12 bit up/down N divider and a digital phase comparator with current source outputs.

The device also has a number of features which increase the design flexibility and performance of the synthesiser. These include fractional-N operation, speed up mode and support of 2, 3 and 4 modulus prescalers. A description of the operation and advantages of each of these features is given.

The main N divider input buffer will accept inputs from an external prescaler, either as balanced (2 wire) ECL levels at frequencies up to 30MHz, or DC coupled to a single ended prescaler output. Single ended operation requires the other buffer input (pin 3) to be externally biased to the correct slicing voltage for the prescaler and also externally decoupled.

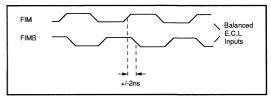

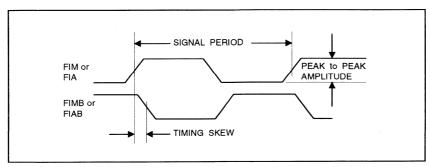

If the inputs are in the form of balanced ECL levels, there must not be a skew of greater than 2ns between one input changing and the second input changing. The relationship of the signals is shown below in Fig.4.

Fig.4 Maximum input skew

The main N divider is programmable so that it can determine how many cycles of each division ratio the external prescaler will perform.

The total division ratio of the output from the system VCO to the synthesiser's phase detector may be expressed as  $N\tau\sigma\tau$  and R1, R2, R3 and R4 are the available prescaler ratios and N1, N2, N3 and N4 are the corresponding number of cycles for each ratio selected, within one complete division cycle.

The divider is programmed via the serial data bus and the values needed to be programmed for each of the possible prescaler ratios are as follows:-

In 2 modulus mode (division ratios R1, R2)

NTOT = N1.R1 + N2.R2

Programmed values needed:

N1 - a 12 bit value giving the number of times R1 is to be used N2 - a 8 bit value giving the number of times R2 is to be used

In 3 modulus mode (division ratios R1, R2, R3)

NTOT = N1.R1 + N2.R2 + N3.R3

Programmed values needed:

N1 - a 12 bit value giving the number of times R1 is to be used N2 - a 4 bit value giving the number of times R2 is to be used N2+N3 - a 4 bit value where N3 is the number of times R3 is to be used and (N2+N3) is modulo-16 addition

In 4 modulus mode (division ratios R1, R2, R3, R4) Ντοτ = N1.R1 + N2.R2 + N3.R3 + N4.R4

Programmed values needed:

N1 - a 12 bit value giving the number of times R1 is to be used N2 - a 4 bit value giving the number of times R2 is to be used N2+N3 - a 4 bit value where N3 is the number of times R3 is to be used.

N2+N3+N4-a 4 bit value where N4 is the number of times R4 is to be used. (N2+N3) and (N2+N3+N4) are modulo-16 addition.

To facilitate the use of multimodulus prescalers the N divider is based upon a twelve bit up/down counter which functions as follows

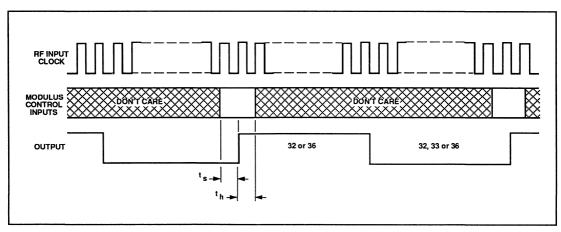

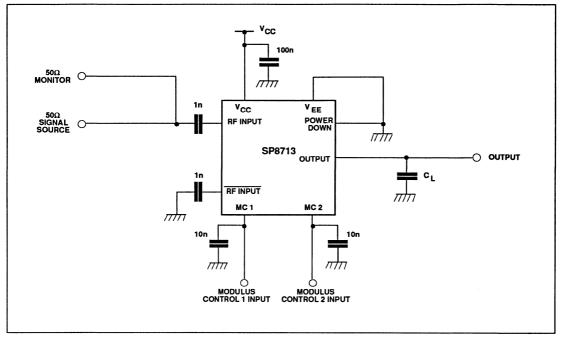

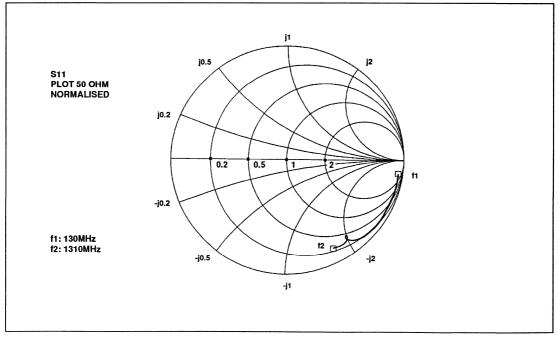

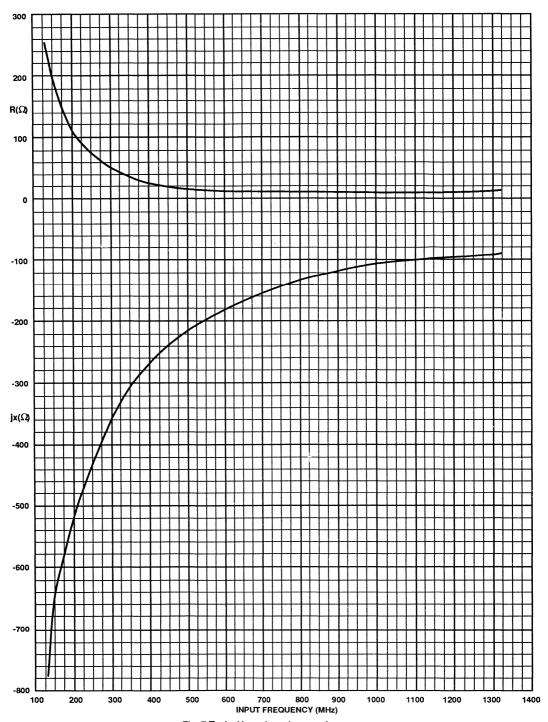

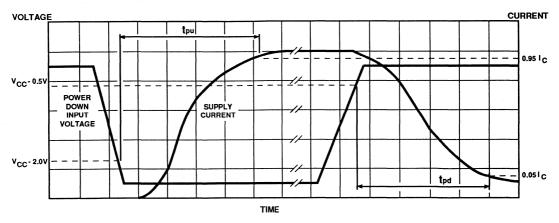

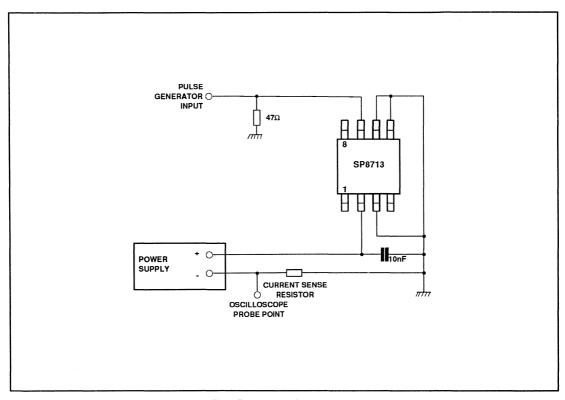

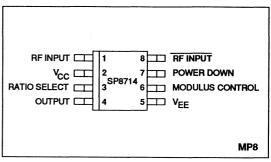

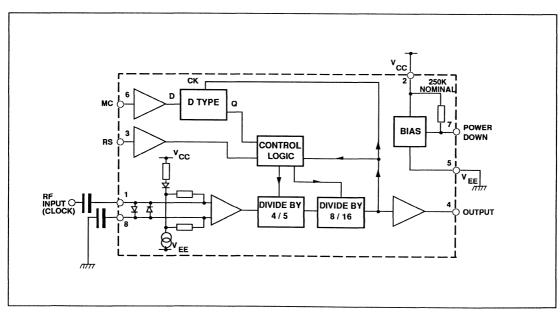

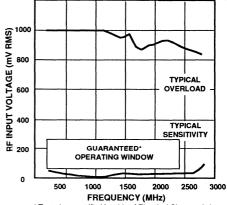

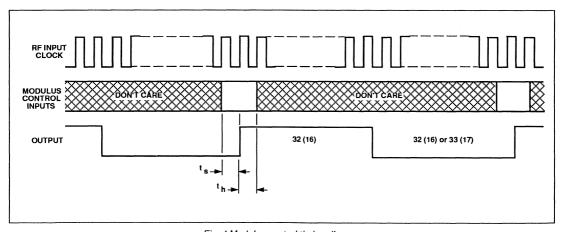

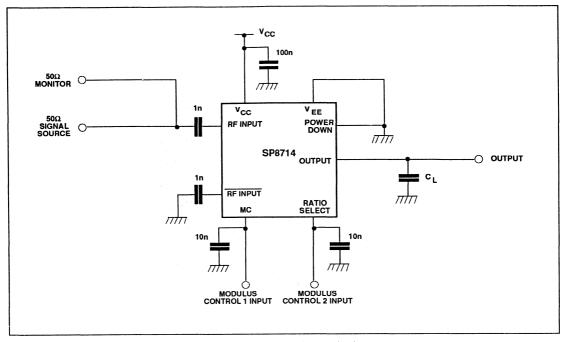

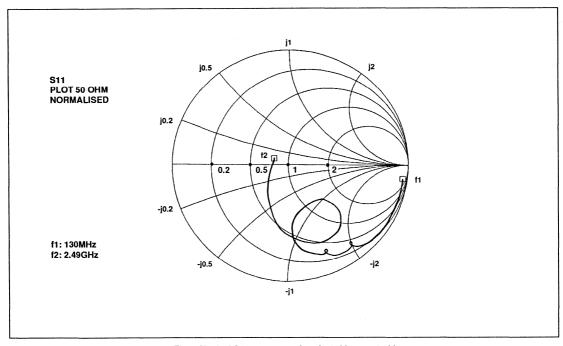

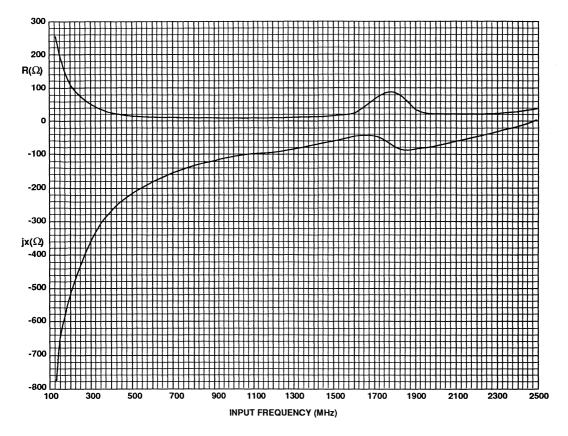

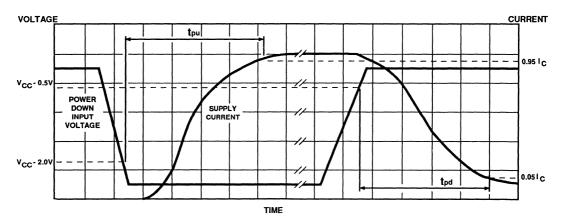

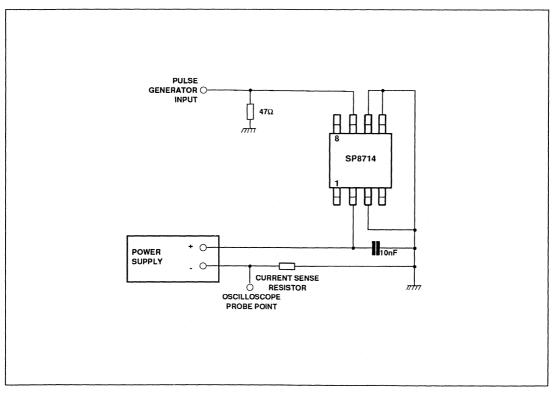

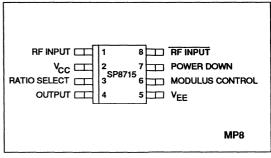

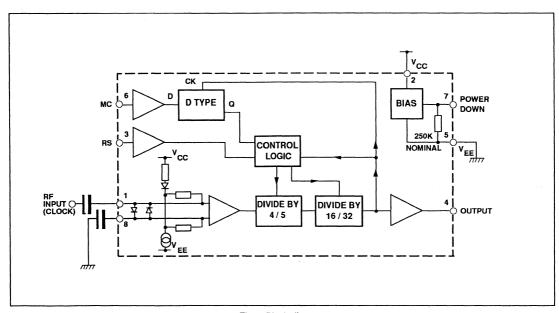

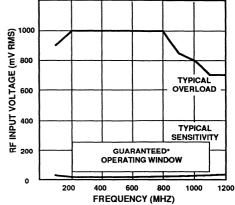

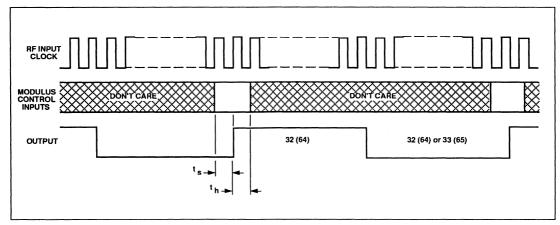

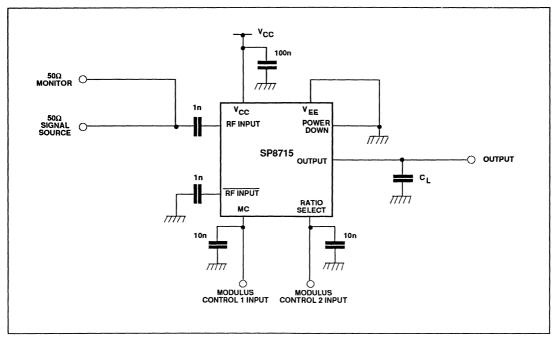

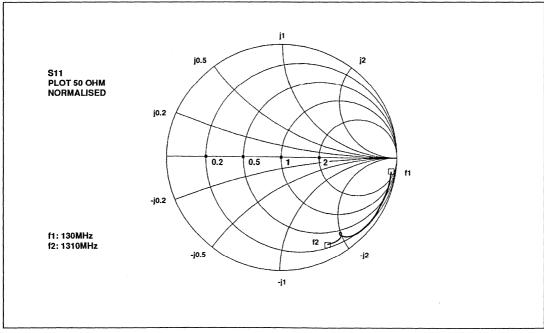

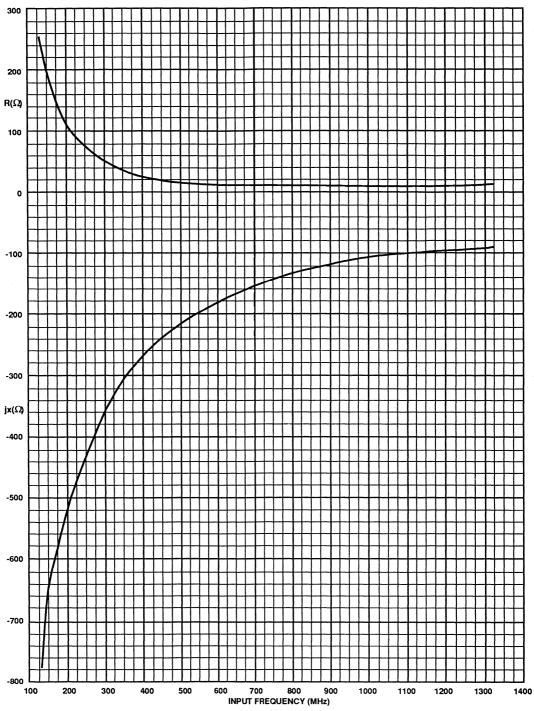

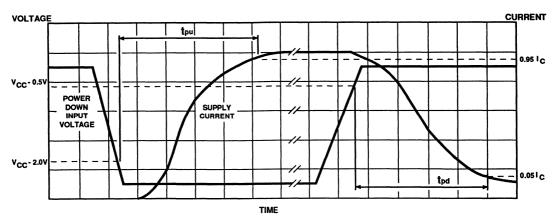

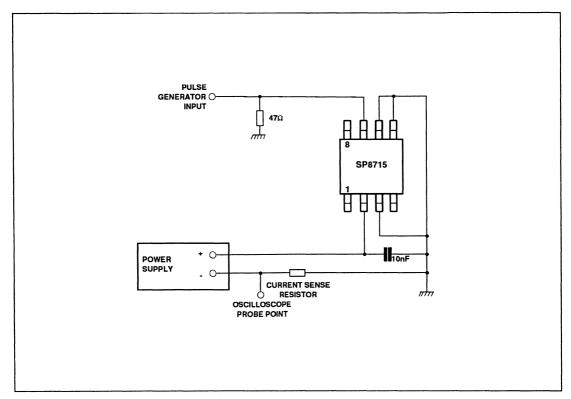

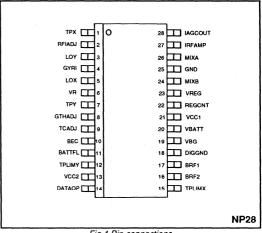

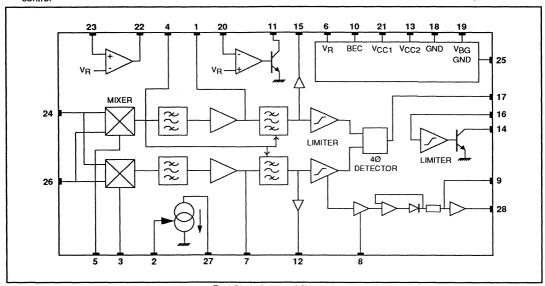

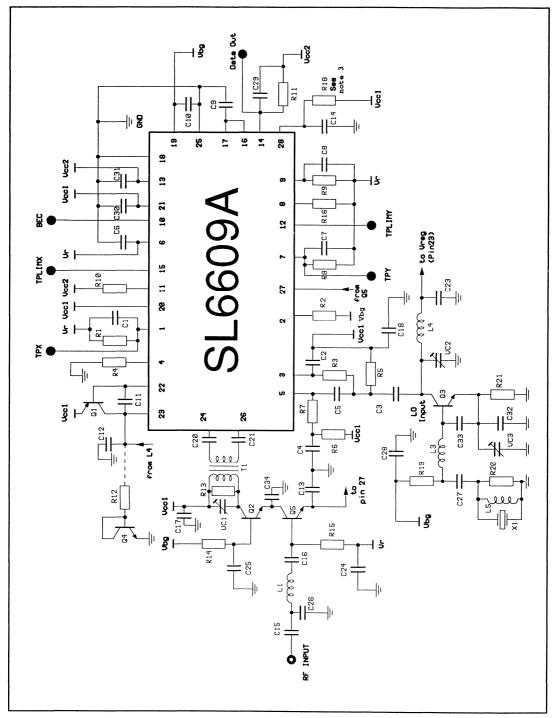

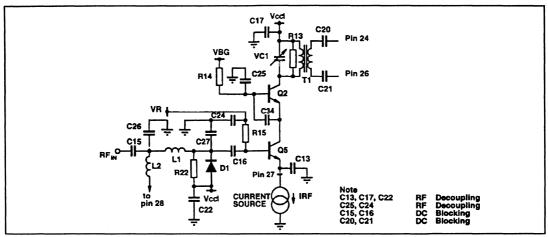

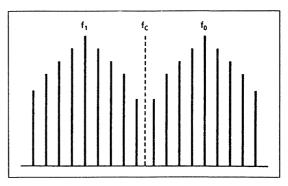

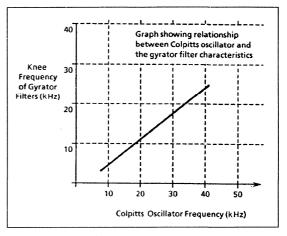

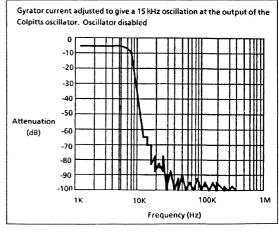

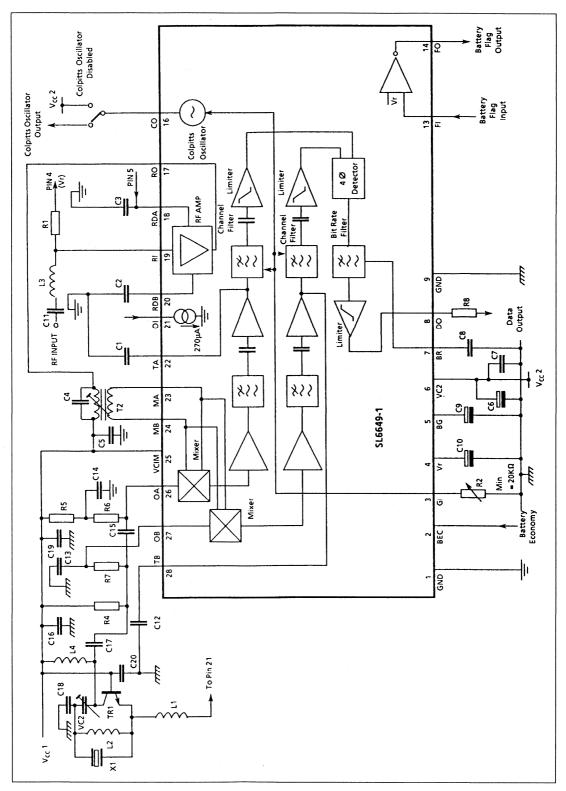

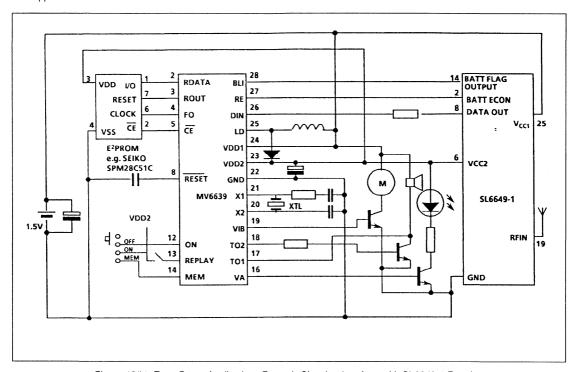

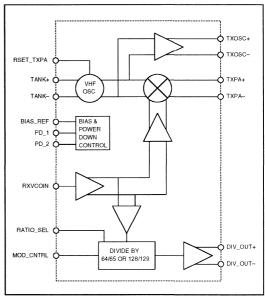

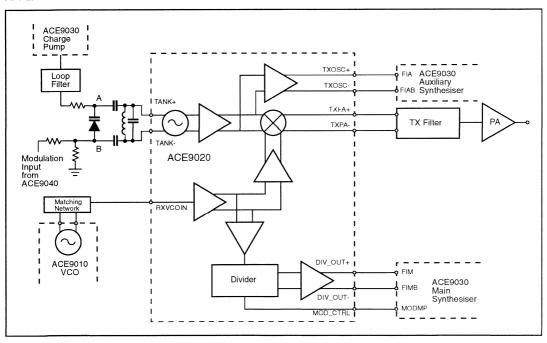

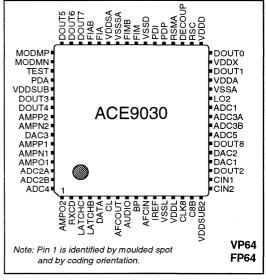

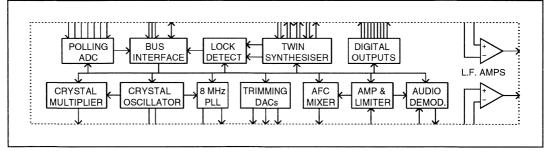

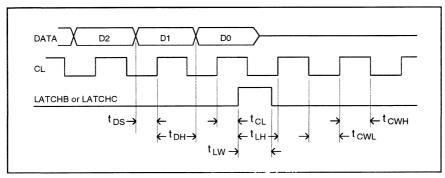

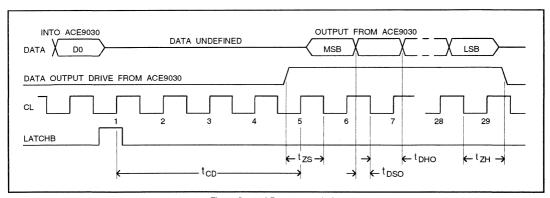

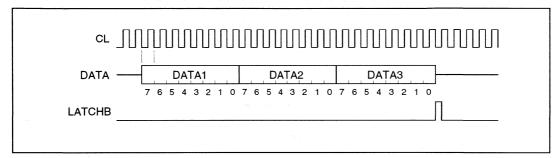

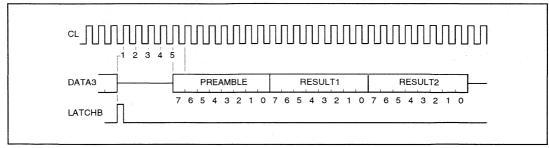

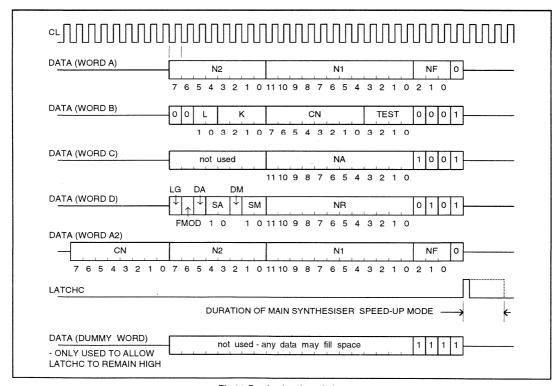

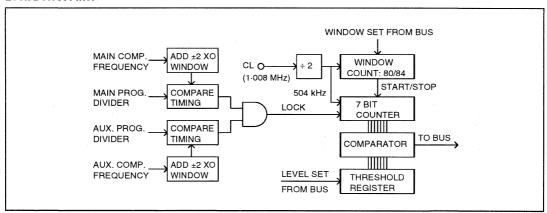

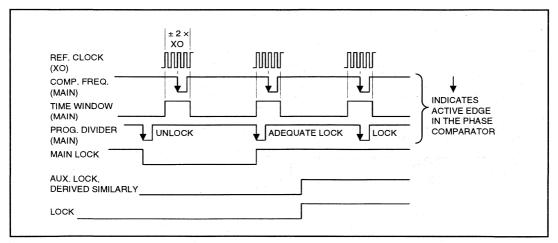

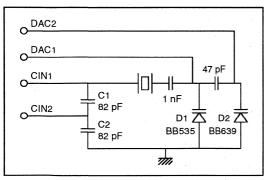

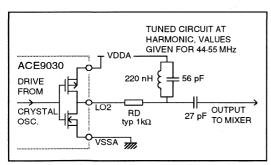

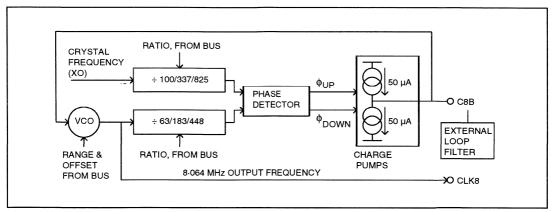

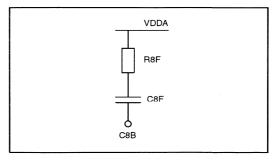

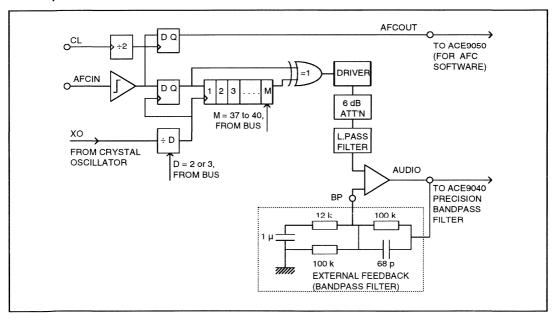

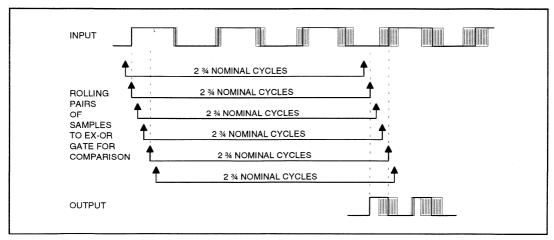

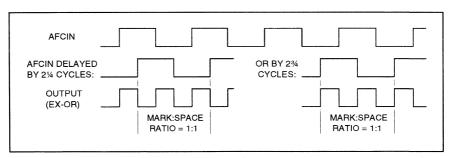

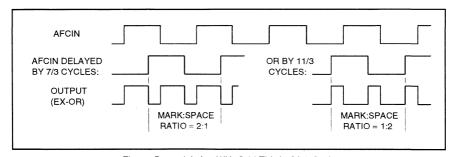

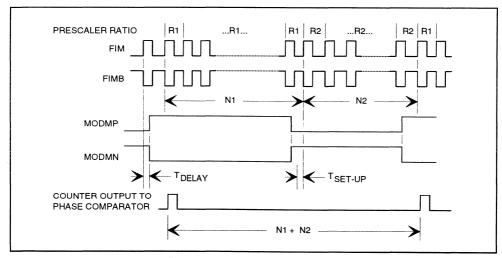

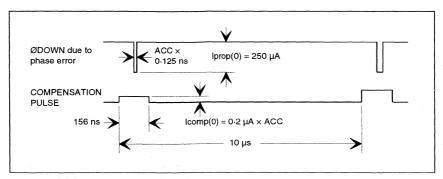

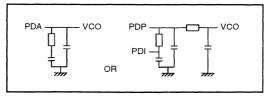

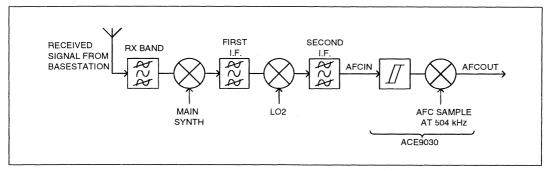

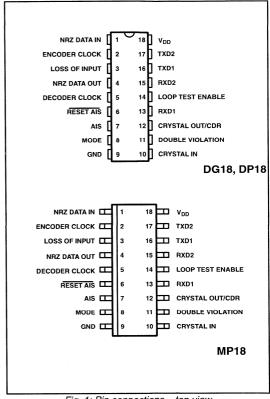

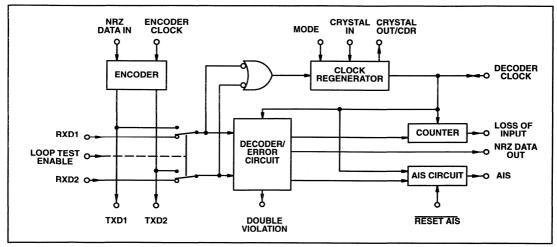

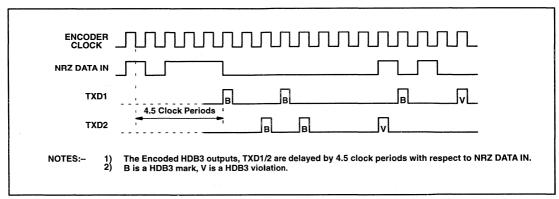

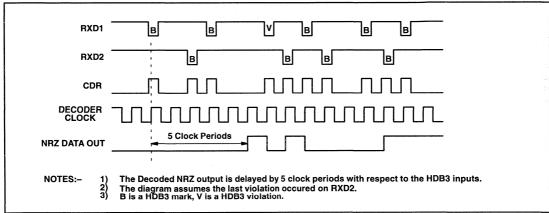

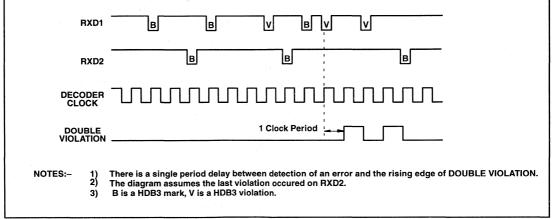

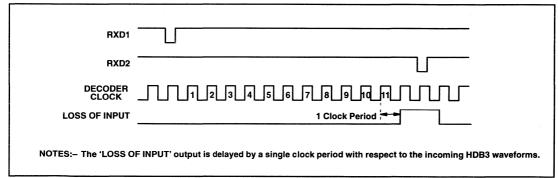

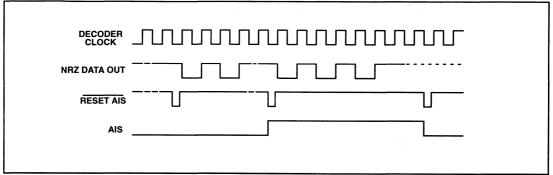

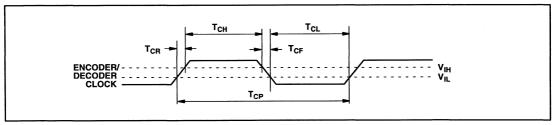

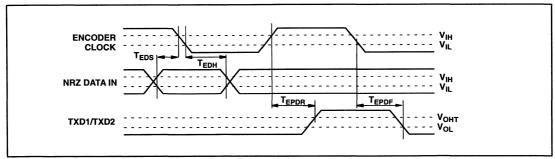

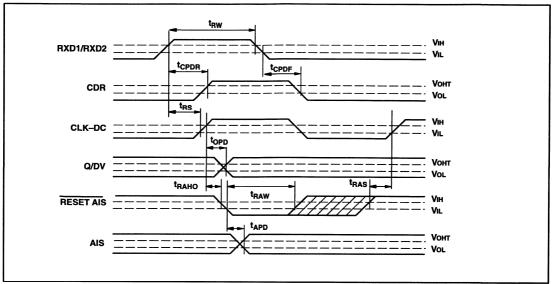

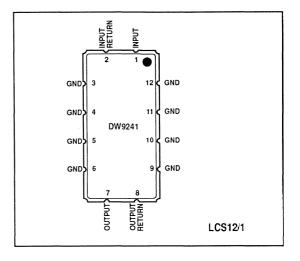

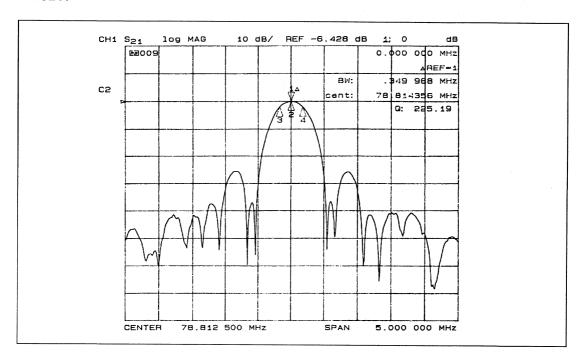

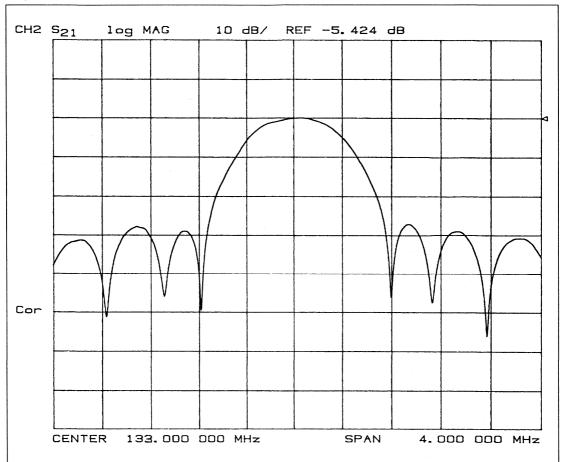

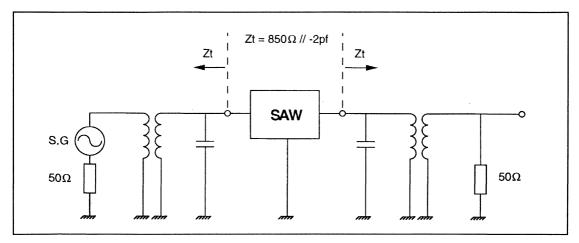

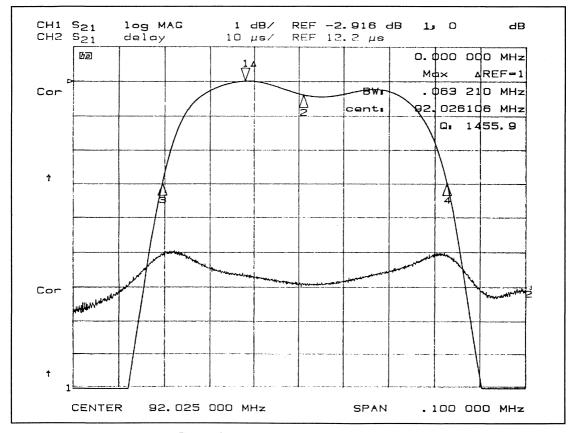

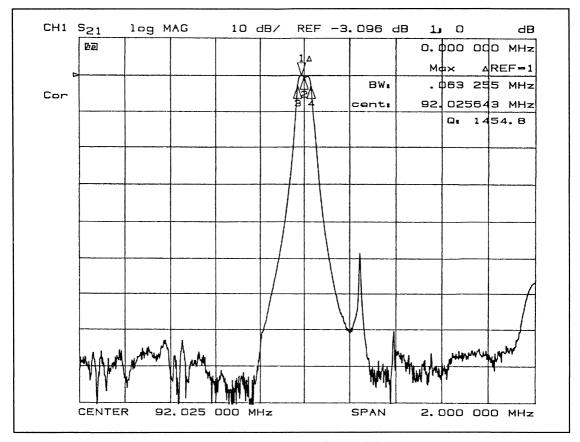

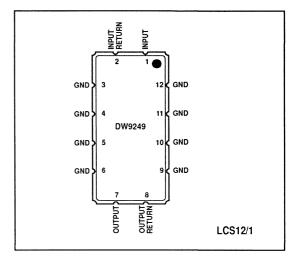

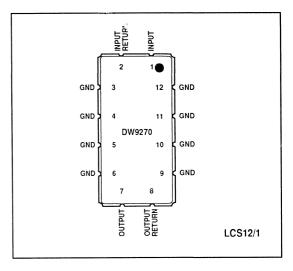

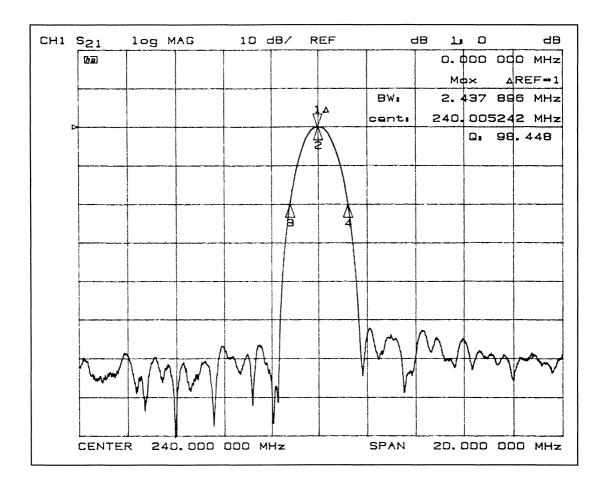

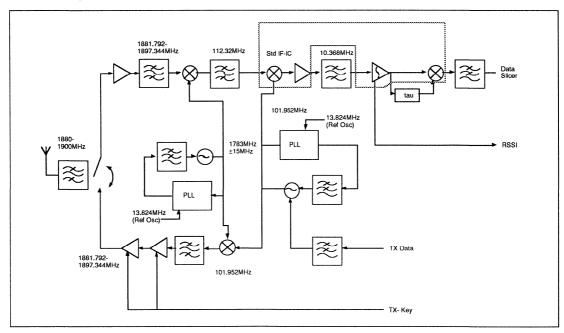

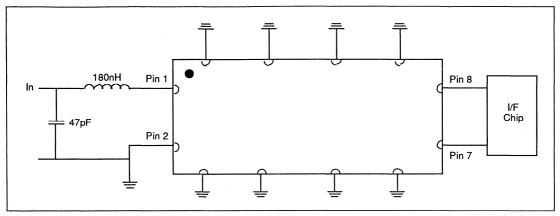

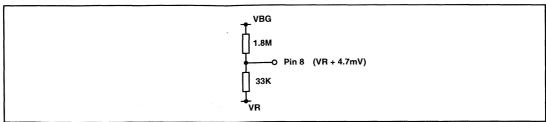

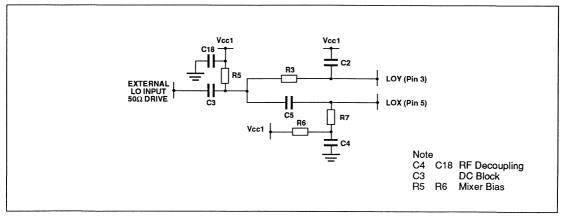

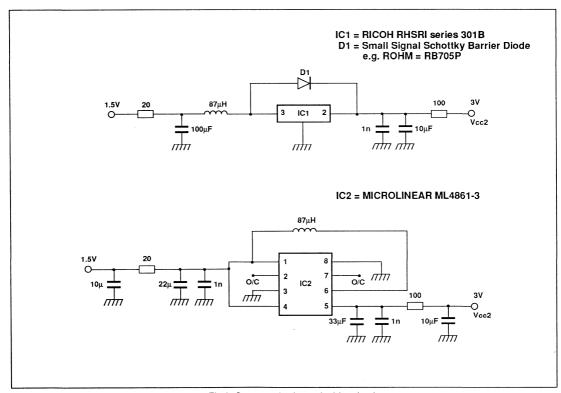

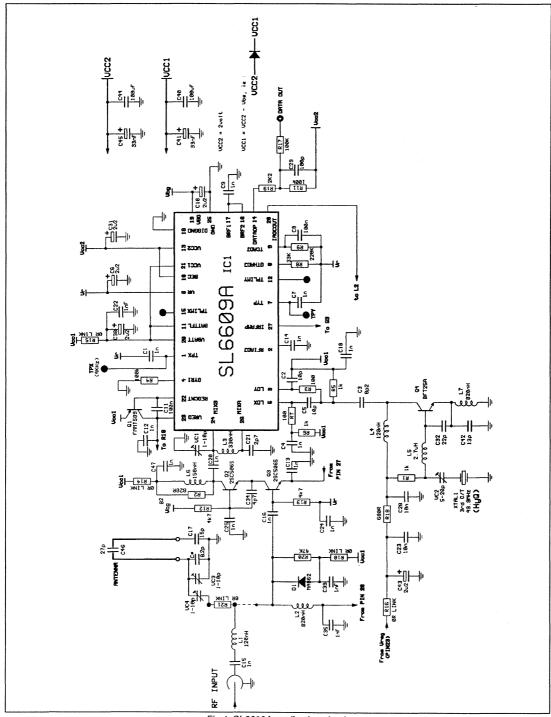

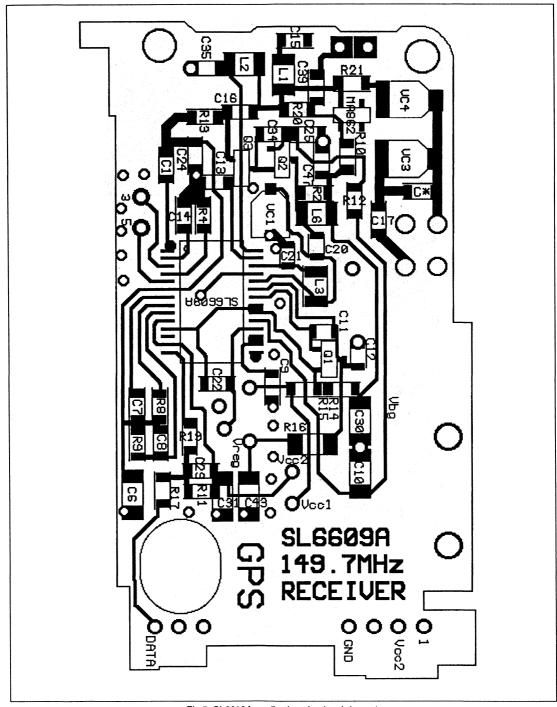

The first value, N1, is loaded into the counter which then counts down from N1 to zero. During this time, the modulus ratio R1 is selected.